## **Digital Electronics**

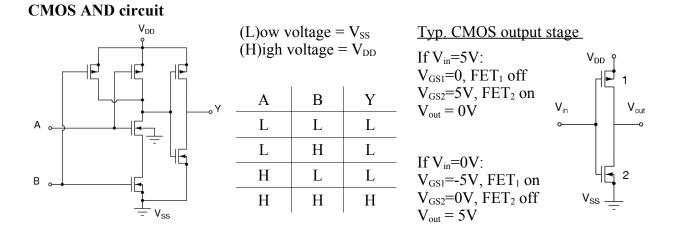

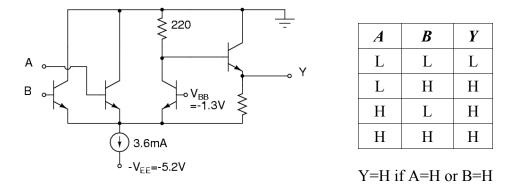

In digital circuits only two values of  $V_{in}$  or  $V_{out}$  are considered, Low (L) or High (H). The two values correspond to the logical states True (T) or False (F).

ECL OR circuit

Standard convention is that L=FALSE=0 and H=TRUE=1 respectively. Logically the above circuits function as logical AND and OR gates respectively.

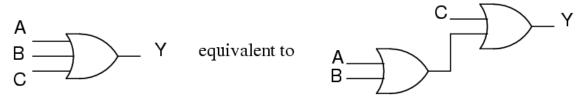

The first identity indicates how a logic gate having more than two inputs should behave, eg:

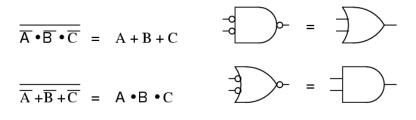

## **De Morgan's Theorem**

If we had identified L voltage with TRUE and H with FALSE, then the NAND and NOR circuits would actually have implemented the OR and AND functions respectively. Interchanging the assignments L=F, H=T to L=T, H=F is equivalent to applying the logical complement to all entries of a truth table...

Note: a circle indicates inversion of a logic level

# **Implementing Logic Equations with Gates**

Take the assignment between voltage levels and logic quantities to be: L = F = 0, H = T = 1Then De Morgan's theorem will be used to treat signals that are "active low."

General problem: Given a truth table, find some combination of logic gates that satisfy the table. The first step is to find a set of logic equations to solve the truth table. There are two ways to do this: (1) by inspection, a.k.a. 'divine intuition', (2) by Karnaugh Map. Then algebraic manipulation can be used to reduce the expression.

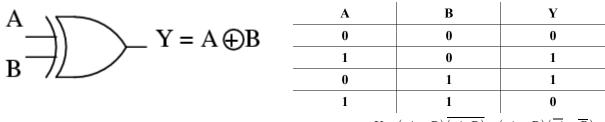

## Example: XOR (exclusive OR) gate

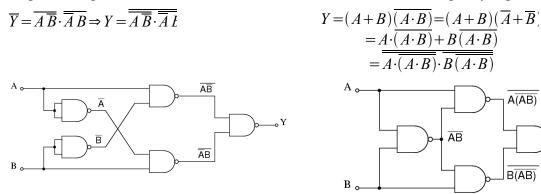

By inspection of the table and using De Morgan's theorem

$$Y = (A+B)\overline{(A \cdot B)} = (A+B)(\overline{A}+\overline{B})$$

$$= A\overline{A} + B\overline{B} + A\overline{B} + \overline{A}B$$

A(AB)

B(AB)

Y

K-Map:

$$\begin{array}{c|c}

A \\

B \\

0 \\

1 \\

\hline

1 \\

\hline

1 \\

\hline

1 \\

\hline

A \\

\overline{AB}

\end{array}$$

$$\Rightarrow Y = A \overline{B} + \overline{A} B$$

Another solution using only 4 gates:

Two implementations using NAND gates  $Y = A \overline{B} + \overline{A} B$

Using De Morgan's Laws:

Note: all logic functions can be built up from NAND gates alone (or from NOR gates).

4

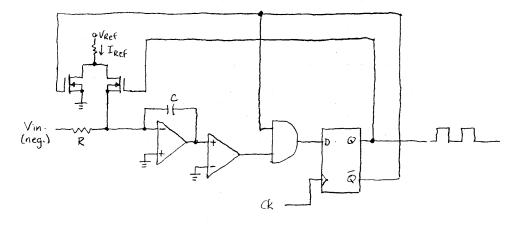

One of the primary uses of digital electronic circuits is to make logical decisions in an experimental situation. an example is the 319 Lab "Muon Lifetime and Magnetic Moment".

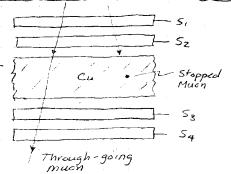

Muons created in the upper atmosphere are detected in scintillators 5, -54 [re particle -> light puke -> photomultiplier tube -> electronic puke -> comparator -> 5n) scendulached around a thick copper black. Most muons pass through the entire stack, leaving a signal in all 4 scintillators. However a few will come to

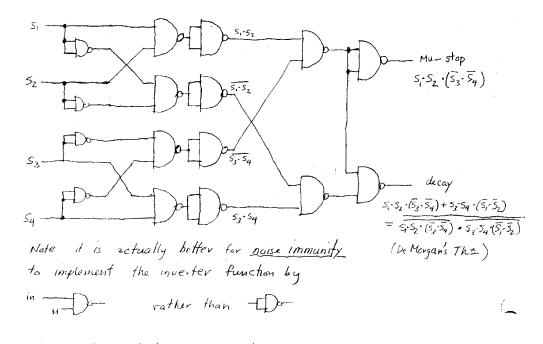

rest in the copper block and these are the ones to study. So, the logic equation describing a much stopping in the block is  $Mu = stop = (S_1 \cdot S_2) \cdot (\overline{S_3} \cdot \overline{S_4})$

After a much comes to rest it will decay into an electron (plus neutrino) within an average ~2.7.45ec. The electron could be detected in this apparatus either going up or down; the logic equations would be.

and E-down = (53.54). (51.52)  $E - up = (S_1 \cdot S_2) \cdot (\overline{S_3} \cdot \overline{S_4})$ The signal of oscilloscope .... in a 4-trace a decay is s \_\_\_\_\_Fl Decay = E-up + E-down 7 5,\_\_\_\_  $\Pi$ Π. Sz \_\_\_\_\_ CT. \_\_\_\_ 54 ..... Through -going décay electron down Stopped Much Muon

tin

10/

implementation of this logic using 2-input NAND gates is

This example illustrates the general result that any logic eq " can be realized by NAND gates alone (although many may be needed, ) If allow the use of other 2-input gates a more compact circuit eg suppore OR gakes are available could be achieved

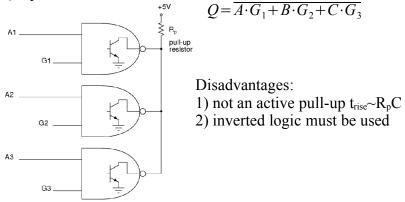

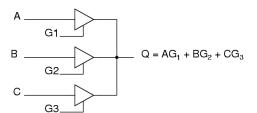

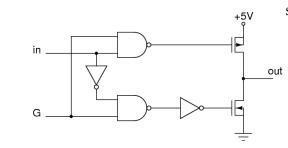

## **Open collector and Tri-State outputs**

In addition to LOW and HIGH output voltage levels, some gates have a third, High-Z, output state. This allows many outputs to be connected together on a single wire (or bus). Two varieties re commonly used:

## 1) Open Collector

2) Tri-State

When both FETs are off (G=0) output is in High-Z state

Relation to Number Codes  $\bigcirc$ In base-2 a number is represented by a sequence of bits (= binary digits) each assuming one of two possible values O or 1. Logic circuits can be used to do binaryarithmetic operations if we identify the logic states L, H with the two possible bit values 0, 1. The representation is similar to base -10, ie there is a digit multiplying each power of the base number MSB LSB  $\begin{array}{c} * \\ 1 \\ 1 \\ 0 \\ 1_{2} \\ \end{array} = 1 \times 2^{\circ} + 0 \times 2^{\prime} + 1 \times 2^{2} + 1 \times 2^{3} = 13_{10} \\ \end{array}$ eg. MSB = most significant bit LSB = least Converting from decimal is accomplished by repeated div. by 2 13/2 = 6– LSB rem 1 6/2 = 3rem 0 i.e. 13, = 1101 3/2 = 1rem 1 \_\_\_ MSB 1/2 = 0rem 1

Arithmetic with unsigned (ie positive only) numbers proceeds just as the base - 10 case

an n-bit sequence has 2° possible values, Thus it can represent the positive integers 0,1,... 2°-1. There are two popular mappings from bit seq, to positive integers;

i) so - called "natural" binary -already used in previous example. ii) Grey code - bit patterns corresponding to successive numbers differ by only one bit. This code is useful in noisy environments.

An n-bit sequence can also be used to represent a range of neg and positive numbers  $-2^{n-1}$ ,  $-2^{n-1}+1$ , ..., -1, 0, 1, ...,  $2^{n-1}-1$ .

The three most popular codes for

representing signed integers are illustrated in the table (taken from  $H \neq H_{BG} = 477$ ).

In the sign/magnitude representation the nth bit is used a sign bit with the others representing the magnitude in "natural" binary - It's not useful for computation

| THREE STOTEMS OF HER RESERVATION |                    |                  |          |  |  |

|----------------------------------|--------------------|------------------|----------|--|--|

| Integer                          | Sign-<br>magnitude | Offset<br>binary | 2's comp |  |  |

| +7                               | 0111               | 1111             | 0111     |  |  |

| +6                               | 0110               | 1110             | 0110     |  |  |

| +5                               | 0101               | 1101             | 0101     |  |  |

| +4                               | 0100               | 1100             | 0100     |  |  |

| +3                               | 0011               | 1011             | 0011     |  |  |

| +2                               | 0010               | 1010             | 0010     |  |  |

| +1                               | 0001               | 1001             | 0001     |  |  |

| 0                                | 0000               | 1000             | 0000     |  |  |

| -1                               | 1001               | 0111             | 1111     |  |  |

| -2                               | 1010               | 0110             | 1110     |  |  |

| -3                               | 1011               | 0101             | 1101     |  |  |

| -4                               | 1100               | 0100             | 1100     |  |  |

| -5                               | 1101               | 0011             | 1011     |  |  |

| -6                               | 1110               | 0010             | 1010     |  |  |

| -7                               | 1111               | 0001             | 1001     |  |  |

| 8                                |                    | 0000             | 1000     |  |  |

| (0)                              | 1000               | -                | -        |  |  |

TABLE 8.1. 4-BIT SIGNED INTEGERS IN

THREE SYSTEMS OF REPRESENTATION

Both Offset Binary and 2's complement Binary have the useful feature that the ordering (in the sense of "natural"

binary) is the same for both positive and negative integers.

Offset-Binary is the natural code to use for Analog , to Digital converters (ADC) and Digital to Analog converters (DAC).

2's - complement binary has the advantage that the same hardware can be used for addition and subtraction, which is just addition of a negative number.

(15) Binary Subtraction To see why the 2's complement representation allows the same hardware to be used for addition and subtraction consider the subtraction of two 4-bit numbers, B minus A. The property of "minus A" should be that A minus A = 0. Note that since the INVERT function converts 0 -1 +1-0. A plus  $\overline{A} = 1111$ => A plus A plus 1 = 10000 Since we are working with only 4-bit numbers the 5th (MSB) must be ignored. => 10000 minus A = Ā plus 1 z's complement.  $B minus A = B plus (\overline{A} plus 1)$ So finally Note this computation will produce a 5th bit which must be discarded. Gate Level Implementation of an Adder Consider first just two bits A and B. The output includes both a sum bit 5 and a carry C, in case A=1 and Bol. Start by writing the truth table out By inspection one can easily see BSC 0 0 5 = A (B (xor) and C= A.B 1 ł 0 0 ( 0 1 0

5

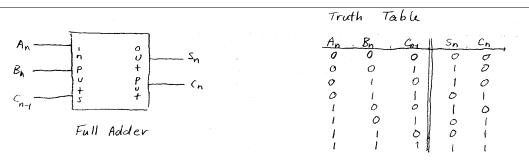

Thus is not a complete adder - in fact it's called a Half Adder A Full-Adder would include a carry-in from a previous stage as an additional input. N such stages could be connected to make an n-bit adder.

Logic eqp follows from the combinations of all inputs yielding an output = 1.

$S_{n} = \overline{A_{n}} \cdot \overline{B_{n}} \cdot C_{n-1} + \overline{A_{n}} \cdot \overline{B_{n}} \cdot \overline{C_{n-1}} + A_{n} \cdot \overline{B_{n}} \cdot \overline{C_{n-1}} + A_{n} \cdot B_{n} \cdot C_{n-1}$  $C_n = \overline{A_n} \cdot B_n \cdot C_{n-1} + A_n \cdot \overline{B_n} \cdot C_{n-1} + A_n \cdot B_n \cdot \overline{C_{n-1}} + A_n \cdot B_n \cdot C_{n-1}$

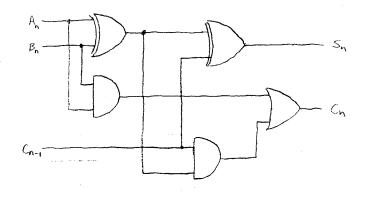

Each term which involves a product of all inputs is called a minterm. The expressions for 5n and Cn are a sum (OR) of minterms - such a form is called standard or canonical form. To reduce these expressions to forms amenable to 2-input gates

use Bockean algebra.

eg.

$$S_n = (\overline{A_n} \cdot \overline{B_n} + A_n \cdot \overline{B_n}) \cdot C_{n-1} + \overline{C_{n-1}} \cdot (\overline{A_n} \cdot \overline{B_n} + A_n \cdot \overline{B_n})$$

$(\overline{A_n + B_n}) + (\overline{A_n} + \overline{B_n})$

$= (A_n \cdot \overline{B_n} + \overline{A_n} \cdot \overline{B_n} + \overline{A_n} \cdot \overline{B_n} + \overline{B_n} \cdot \overline{B_n})$

$\Rightarrow S_n = C_{n-1} \cdot (\overline{A_n \oplus B_n}) + \overline{C_{n-1}} \cdot (A_n \oplus B_n) = C_{n-1} \oplus (A_n \oplus B_n)$

The motivation for manipulating the fermi to look like

$X \circ R$  is came from the observation of an  $X \circ R$  in the

Half Adder circuit.

By inspection of the Full-Adder's Truth Table, a carry-cut Cn occurs when two or more of the inputs = 1. This could be described by, Cn = Bn·Cn-1 + Cn-1·An + An·Bn + An·Bh·Cn-1. Eq<sup>th</sup> would require 5 more gates.... However working directly from the previous  $eq^{th}$  a more compact implementation can be achieved  $Cn = \overline{An} \cdot Bn \cdot Cn-1 + An \cdot \overline{Bn} - (\overline{Cn} + Cn)$   $= (\overline{An} \cdot Bn + An \cdot \overline{Bn}) \cdot Cn-1 + An \cdot Bn$  $= (P_n \oplus B_n) \cdot Cn-1 + An \cdot Bn$

Note the implementation is not unique. eg. the student manual uses 2 ANDs & 2 ORs to form Cn. If one were required to use only AND & OR the implementation would have been even more different.

Ø

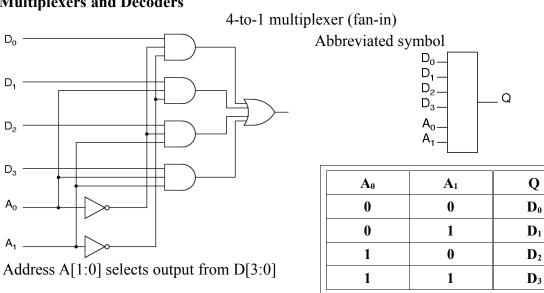

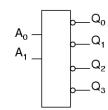

| $A_0$ | A <sub>1</sub> | Q <sub>0</sub> | $\mathbf{Q}_1$ | $\mathbf{Q}_2$ | <b>Q</b> <sub>3</sub> |

|-------|----------------|----------------|----------------|----------------|-----------------------|

| 0     | 0              | 0              | 1              | 1              | 1                     |

| 0     | 1              | 1              | 0              | 1              | 1                     |

| 1     | 0              | 1              | 1              | 0              | 1                     |

| 1     | 1              | 1              | 1              | 1              | 0                     |

Address A[1:0] clears one bit from Q[3:0]

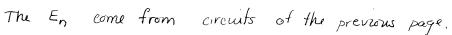

Both can be used to implement arbitrary functions of two boolean variables (bits) Often these devices have enable inputs for tristate outputs.

# Multiplexers and Decoders

Digital

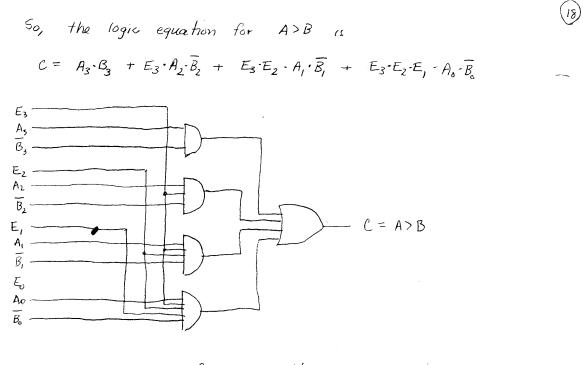

(19)

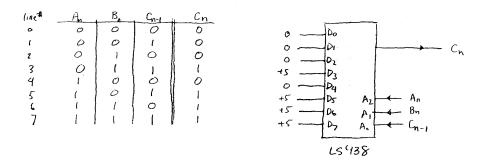

# Implementing Arbitrary Logic Eques W a Multiplexer

"The quick & dirty solution".... An example will illustrate the technique. Suppose you wanted to implement the carryout logic of the Full Adder without going through any logic minimization. => Apply inputs to address line of a multiplexer and set D lines high or low corresponding to the line of the truth table

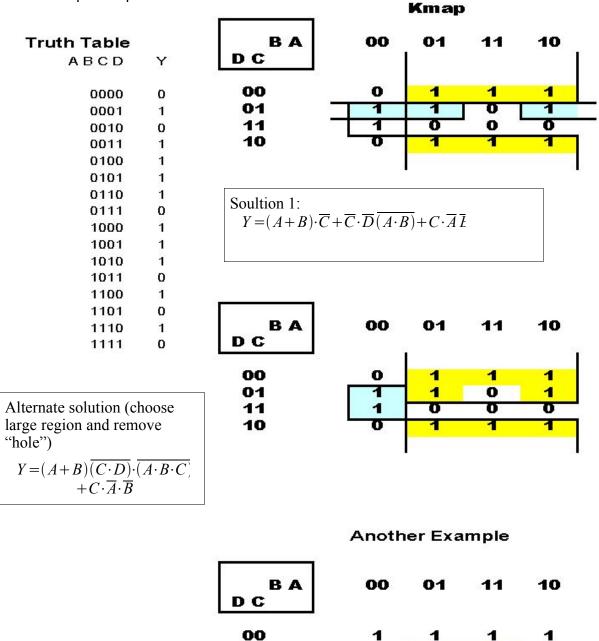

## Karnaugh Maps

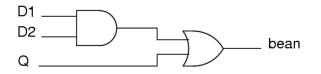

The Karnaugh map or K-map offers a convenient way to visualize logic equations from a truth table. Consider the following logic problem:

We have a chocolate-covered coffee bean machine, that returns a bean for a 20 cent fee. The machine accepts only quarters and dimes. To make matters simple, we'll ignore the job of making change. To enter the fee, assume the machine has a drawer w/ three depressions, one for a quarter and two for dimes (like many coin-op washing machines).

Obviously, a single quarter or two dimes will satisfy the fee requirement to get a bean. The truth table (for all possible input combinations) is:

| Q | D1 | D2 | bean |

|---|----|----|------|

| 0 | 0  | 0  | 0    |

| 0 | 0  | 1  | 0    |

| 0 | 1  | 0  | 0    |

| 0 | 1  | 1  | 1    |

| 1 | 0  | 0  | 1    |

| 1 | 0  | 1  | 1    |

| 1 | 1  | 0  | 1    |

| 1 | 1  | 1  | 1    |

|   |    |    | 1    |

|   |    |    |      |

K-map for bean machine:

(note: grey code must used in all row/ columns)

| $Q \setminus D_1 D_2$                 | 00 | 01 | 11               | 10 |    |

|---------------------------------------|----|----|------------------|----|----|

| 0                                     | 0  | 0  | 1                | 0  |    |

| 1                                     | 1  | 1  | 1                | 1  | =Q |

|                                       |    |    | $=D_1 \cdot D_2$ |    |    |

| Therefore: $bean = Q + D_1 \cdot D_2$ |    |    |                  |    |    |

Digital

Phys 315/519

## Digital

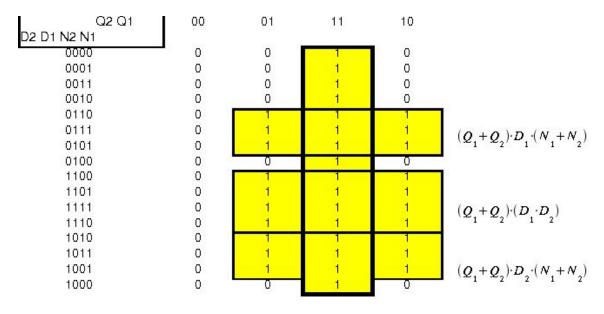

A slightly more detailed example.

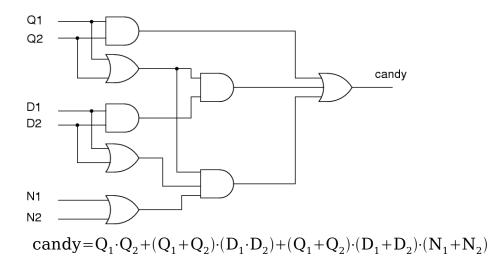

Now we have a vending machine that takes up to 6 coins (2Q, 2D, 2N). Candy may be returned if at least 40 cents is input, gum may be returned if at least 30 cents is input. Let's look at the Kmap for candy:

$Q_1 Q_2$

More K-Map Examples:

1

O

O

1

(20)

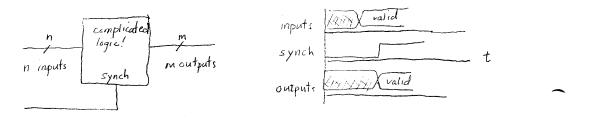

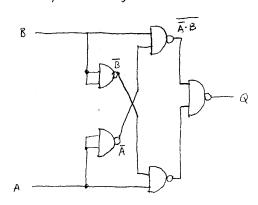

Logic Race Conditions

This describes a transient (~10ns) wrong output state. Occurs because

- 2) internal propagation delays may not be matched for different inputs

- ii) input signals may not be applied simultaneously (precisely)

\* iii) Logic circuit outputs respond continuously in time according to inputs.

Although one can't do much about items i) 4 ii), by designing circuits whose outputs change only when a synchronization signal is applied one can avoid Logic race condition. This type of logic is called sequential logic - described later.

Example of logic race in XOR

Even though gate propagation delays might be matched, the extra gate delay needed for  $\overline{A}$ ,  $\overline{B}$  causes glitch at output.

211

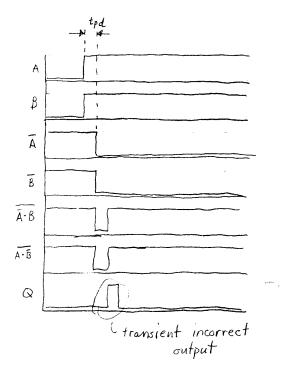

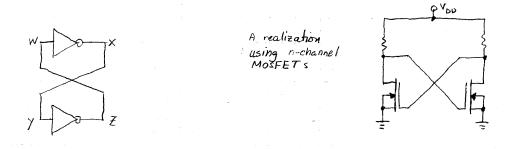

#### Sequential Logic

In combinational logic circuits the outputs depend only on the present (or Tpd earlier) inputs. It is convenient to be able to store the outputs of a combinational circuit for use later in succeeding steps of some complicated algorithm. Logic circuits having memory are called sequential circuits. In general their outputs depend on previous autputs as well as perhaps present inputs. Past 4 present are sometimes delineated by a synchronizing, or clock, signal,

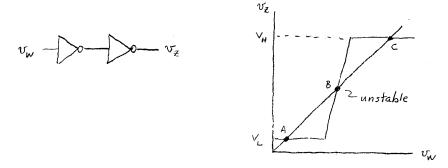

The most basic memory element is a <u>bistable latch</u> made from two inverters

By breaking the Z-W feedback, but using the constraint  $v_{w} = v_{\overline{z}}$ one can see that there are 3 equilibrium points, two of which are stable (A+C) and one unstable (B)

Consider the unstable point B. Refer incremental voltages vi etc about that point. In any circuit there is unavoidable noise

- i

which in this case appears as an initial value  $v_w(0) \neq 0$ . This disturbance is amplified and after a propagation-delaytime  $\tau$  appears at the output  $v_2(t) = G v_w(t-\tau)$ . Now when the feedback is re-established  $v_2(t) = G v_2(t-\tau)$  $\vdots = v_x(t) \approx v_w(0) e^{\frac{t}{2}}$

This result, that the operating point rapidly moves to either points A or C relies only on G>>1 and  $z \le mall$  which is the usual case. The stability of points A and C follow because the incremental gam  $G \rightarrow 0$ . {i.e.  $v_2 = (G-1)v_2 + G-1 < 0$ }

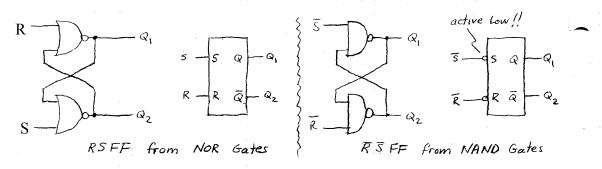

To make the bistable circuit useful we need a way to force into one of the stable states. The simplest realization of this is the Set/Reset Flip Flop (RSFF).

| S | R | $R_1 = Q_2$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|---|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0 | 0 | O     "MEM" previous<br>values held.<br>The input condution (SR)= (1,1)<br>should be avoided since upon                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 0 | a | 1 0) values neld. should be avoided since upon                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| σ | 1 | 0 1 "RESET"<br>1 0 "SET"<br>0 0 * avoid!<br>1 0 * |

| 1 | о | 1 0 "SET"   state SET or RESET will                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 1 | 1 | 0 0 * avoid! be unpredictable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|   |   | Note that in normal operation $Q_2 = \overline{Q_1}$<br>in the MEM state                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

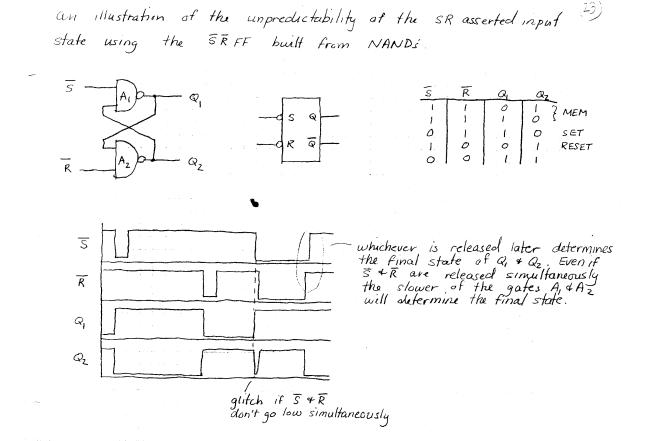

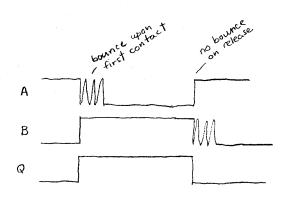

The RSFF is the basis of more complicated and useful Flip Flops. Nevertheless the simple two gate circuit has some applications

Digital

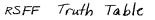

There are two problems with the simple RSFF that prevent 25/ its use in more complicated circuits

i) S & R need to change simultaneously

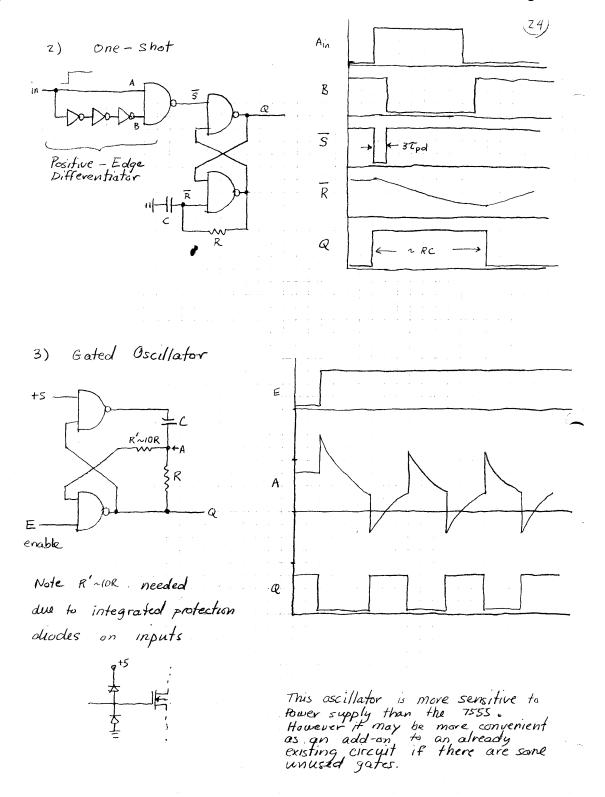

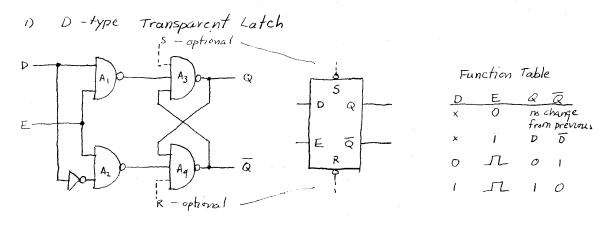

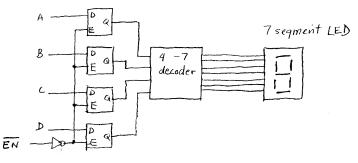

Two circuits which address these problems (- not completely)

E

$$q=D \longrightarrow q = value of D just before end of pulse \rightarrow$$

This kind of Latch is found in the HP dislays used in lab.

Digital

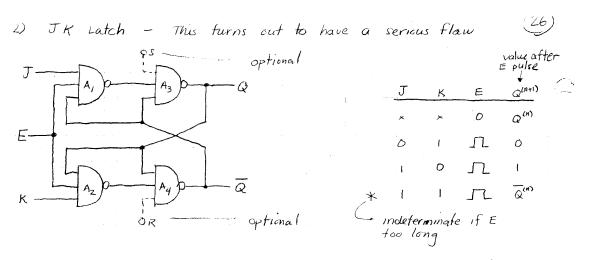

Again a synchonization pulse  $E = \int \sum_{i=1}^{n} is$  used to insure that inputs to  $A_3 \neq A_4$  change simultaneously. The asynchronous (optional) set and Reset act independent of E and, in general, should only be used to define initial conditions. The function table can be verified from the truth table below which gives  $\mathcal{Q}^{n+1}$  the output just after Epulse for the input cond<sup>m</sup>  $\mathcal{J}^{(n)}$ ,  $\mathcal{K}^{(n)}$ , ... existing just before the end of  $\mathcal{J}^{(n)} \xrightarrow{\mathcal{K}^{(n)} \mathcal{Q}^{(n)}} \xrightarrow{\mathcal{Q}^{(n)} \mathcal{Q}^{(n)}} \mathcal{Q}^{(n)}$  "Hold" the Epulse.

| For JK Latch  | k. | 0   | σ | 1 | $\left\{\begin{array}{c}1\\a\\m\end{array}\right\}$ |  |

|---------------|----|-----|---|---|-----------------------------------------------------|--|

| Sfor JK Latch | ł  | 0   | 1 | 0 | Q                                                   |  |

| ()            | 0  | 1   | 0 | 1 | Q <sup>m</sup> } )                                  |  |

|               | D  | .1  | 1 | 0 | 0 ] 0                                               |  |

|               | 1  | . 1 | 0 | 1 | } Q " Toggle"                                       |  |

|               | (  | . 1 | 1 | 0 | 0 } Q :03].0                                        |  |

|               |    |     |   | • |                                                     |  |

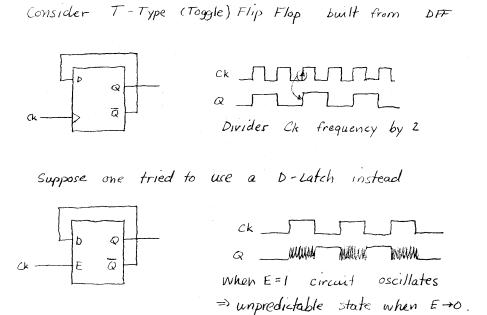

Note a race - around condition accurs when J=k=E=1; the eircuit will oscillate between  $Q\overline{Q} = (01)$  and (10) with period ~2Tpd!! When  $E \rightarrow 0$  it is indeterminate which state the circuit will end up in . A way to avoid this is to insure that the E pulse is very short, eq. use edge detector from pg 24

configuration ..

3

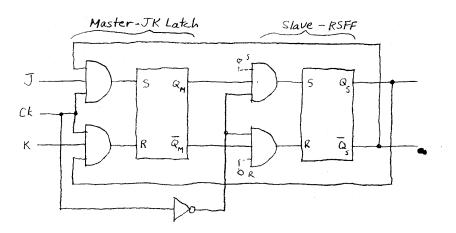

Master - Slave JK Flip Flop

The oscillation problem in the Toggle state of the JK latch can be cured by breaking the feedback wy the Master-Slave

When Ck=1 the master is enabled and it follows the JK latch Truth Table with  $Q^{(n)}$  being provided by the slave outputs  $Q_s$ . When Ck=0 the master holds and the slave responds of  $Q_m$  as input according to the RSFF table on pg 22. Therefore the Master-Slave JKFF follows the function table at the top of pg 26. Note that the outputs change only on the Negative-going edge of the clock Ck.

However there is still a problem with this circuit! J and K must remain constant during Ck pulse otherwise the inputs before the pulse => state after pulse according to table. eg. suppose K=O and the following seq.

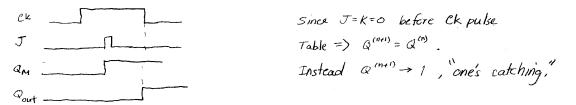

Edge - Triggered Flip Flops

Generally these are the most convenient to apply, compared to the level sensitive types (D latch JK latch) and M/S configurations, because the output changes <u>after</u> a clock edge according to the input(s) present just <u>before</u> the clock edge. Two major types used in our Lab.

1) Positive-Edge Triggered D-type Flip Flop

Note: i) Output changes only on the positive sloping edge of ck, ii) S + R overide Ck, they act shortly after applied independent of Ck. (This is called asynchronous) the inversion symbol is nears the specified action takes place when signal is low is S=0 to set Q = 1.

iii) Set up and Hold times D (1)

- T

(30)

1-

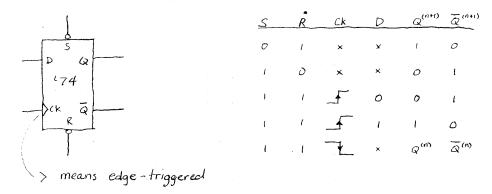

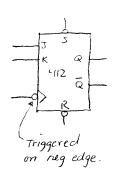

- 2) Negative Edge Triggered JK Flip Flop

| 5 | R | J | ĸ | Ck         | (n+i)                                                  |

|---|---|---|---|------------|--------------------------------------------------------|

| Ð | t | × | × | *          | 0                                                      |

| l | 0 | × | × | *          | 1                                                      |

| ( | Ţ | 0 | I | £          | 0                                                      |

| I | 1 | ł | ð | Ł          | l                                                      |

| l | 1 | 0 | О | Z          | Q (n) "Hold"                                           |

| 1 | 1 | 1 | I | - <b>T</b> | Q <sup>(n)</sup> "Hold"<br>Q <sup>(n)</sup> . "Toggle" |

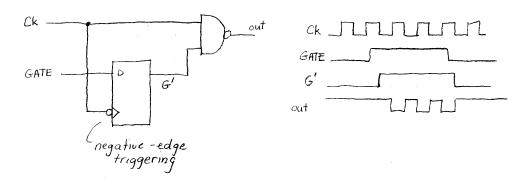

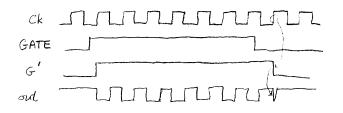

A better synchronizer would have GATE changing only while Ck = 0 since then the output is definitely High.

Note if one instead used a positive - edge triggered FF there would always be a glitch at the end of GATE because G' goes low slightly after CK

Ck

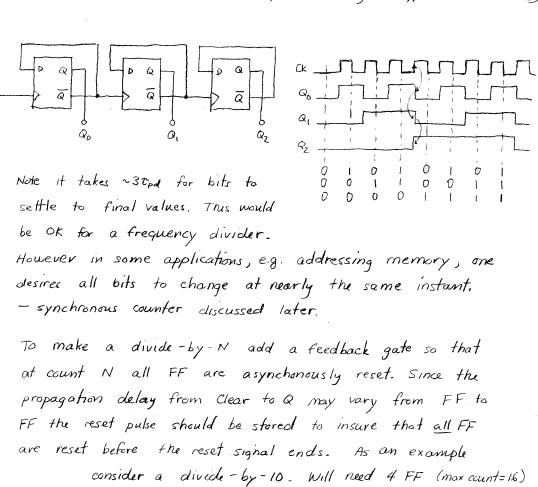

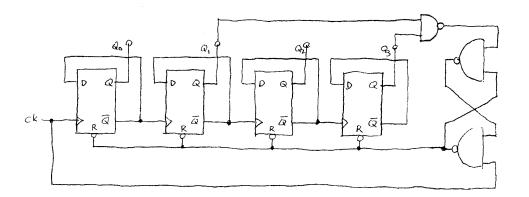

2) <u>kipple Counter</u> - counts Ck pulses using T-type FF

Digital

(32)

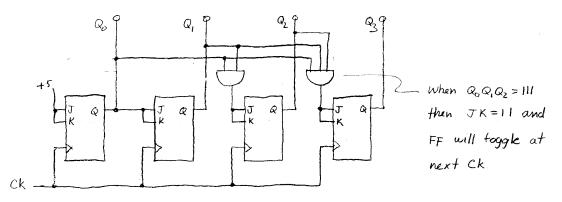

| 10010        |                                   |

|--------------|-----------------------------------|

| 0011<br>0100 | $Q_m$ toggles only when $Q_i = 1$ |

|              | for all z < m,                    |

|              |                                   |

- It turns out to easiest to realize this w/ JF Flip Flops' since they toggle or hold based on JK inputs.

Note that ideally all Q= change simultaneously when Ck I. Therefore a divide-by-n made with a synchronous counter will operate at much higher frequency than w/ ripple counter.

(34)

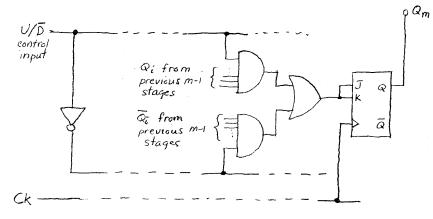

- "Direction" Up/Down Control

From the counting sequence one can see that the rule for counting down is  $Q_m$  toggles when all previous  $Q_j = 0$ . So the logic for driving the JK inputs for the  $m^{th}$  FF would look like

U/D must be asserted some "set up time" to before Ckt in order to work properly.

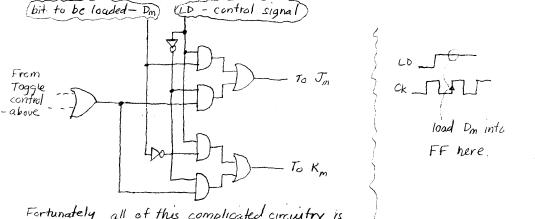

- Parallel Load

Allows you to preset the counter to a particular value. Can be synchronous in takes effect when CKt or asynchronous in takes effect immediately. An example of synchronous loading the JK inputs might lock like;

Fortunately all of this complicated circuitry is inside the IC!

(35)

- IC Counter Features c'ta

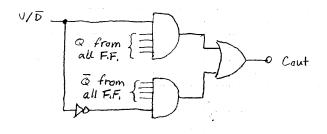

- Carry-in (Cin) and Carry-out (Cout) These are primarily used for connecting two IC n-bit counters to make a 2n-bit counter,

- i) If Cin is False then counting should be inhibited. Internally it might look like cin

ii) Cout is an output which is true when the terminal count of the counter is reached, is O it counting down.

Making a 2n-bit counter out of two n-bit counters is usually this simple

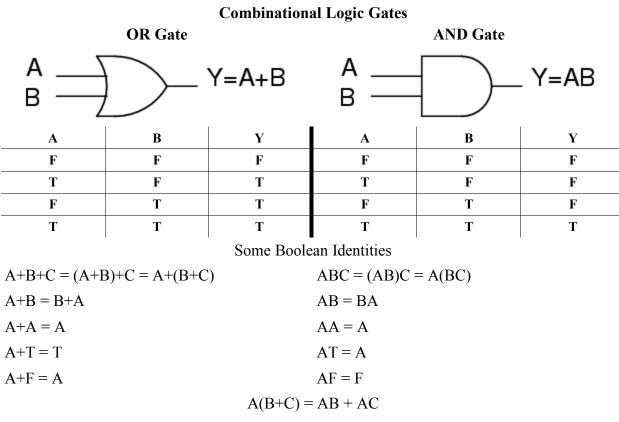

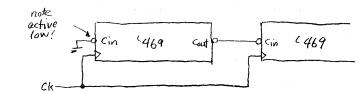

Counters are useful in measurement if the physical quantity to be measured can be "converted" into a pulse whose duration is ac to the value of the quantity. A counter then counts the number of Clock "ticks" (Ck1) during the pulse.

The example built in Lab is a capacitance meter

Count Clocks while our=LOW => <\* measurement,

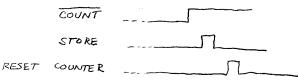

The main detail that one needs to take care of is how to store the count at the end of one measurement cycle reset the counter for the next cycle. The desired pulse sequence looks like

Note if the storage register is edge sensitive. STORE and RESET could occur at the same time if the required hold time of the register's FF = O. If the register is level sensitive you must have RESET occurring later to avoid STORE ing zero! In the Lab the necessary delay and pulse formation is achieved with a shift register RESET Ck JULUL COUNT ā COUNT rk STORE RESET STORE

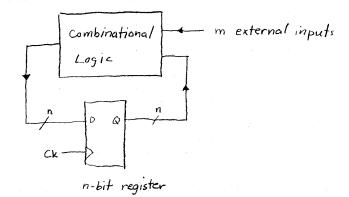

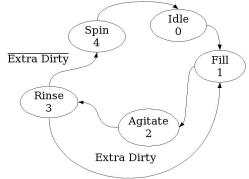

## State Machines

A collection of n flip-flops (n-bit register) can have 2" possible states is values of  $Q_0, Q_1, Q_2, \dots, Q_n$ . A state machine is a clocked digital system whose  $\{Q_i\}$  move through the state space. The trajectory may be determined by the  $\{Q_i\}$ , external inputs or both. In the former, more restrictive, case the trajectory is clased is it repeats. This is a generalized counter. The latter case is somewhat like a computer.

The general architecture of a state machine is

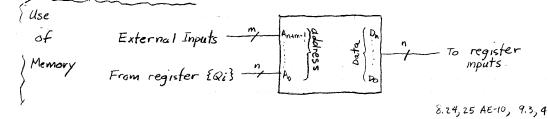

Note i) It is important that the register be edge triggered so that { Qi } remain constant while all signals propagate through the combinational logic.

ii) The combinational logic could be replaced by either n (n+m)-line multiplexers (see ps 19) or a 2<sup>n+m</sup> (address) × n-bit memory. The latter is more general bat is usually somewhat slower than the decoders or using combinational logic.

(31)

Phys 315/519

Digital

We can think of a state machine as somewhat like counter with 2<sup>n</sup> possible values, but state machine can progress in a more general way (not limitied to monotonic progressions).

Example: washing machine

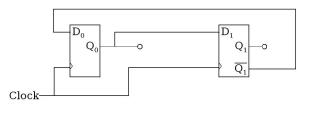

# First detailed example: 2-bit gray code counter

Count progression is: 00, 01, 11, 10, 00, ... These represent out states and their relative ordering.

To construct this device: write a truth table for input/outputs: inputs=current stare info, outputs = next state info.

Devise necessary logic from the T Table to generate D's from Q's:

$$\begin{array}{l} \mathbf{D}_{0} = \overline{\mathbf{Q}_{1}} \overline{\mathbf{Q}_{0}} + \overline{\mathbf{Q}_{1}} \mathbf{Q}_{0} = \overline{\mathbf{Q}_{1}} \cdot (\overline{\mathbf{Q}_{0}} + \mathbf{Q}_{0}) = \overline{\mathbf{Q}_{1}} \\ \mathbf{D}_{1} = \overline{\mathbf{Q}_{1}} \mathbf{Q}_{0} + \mathbf{Q}_{1} \mathbf{Q}_{0} = \mathbf{Q}_{0} \cdot (\overline{\mathbf{Q}_{1}} + \mathbf{Q}_{1}) = \mathbf{Q}_{0} \end{array}$$

| Previous Q <sub>i</sub><br>input for comb <sup>n</sup> logic |              |    |    | $\begin{array}{c} \text{Next } \textbf{Q}_i \\ \text{output of comb^n logic} \end{array}$ |    |                   |  |  |

|--------------------------------------------------------------|--------------|----|----|-------------------------------------------------------------------------------------------|----|-------------------|--|--|

|                                                              |              | Q1 | Q0 | D1                                                                                        | D0 | _                 |  |  |

|                                                              | State -<br>0 | 0  | 0  | 0                                                                                         | 1  | These are the     |  |  |

|                                                              | 1            | 0  | 1  | 1                                                                                         | 1  | inputs we need to |  |  |

| e                                                            | 2            | 1  | 1  | 1                                                                                         | 0  | get to the next   |  |  |

|                                                              | 3            | 1  | 0  | 0                                                                                         | 0  | state             |  |  |

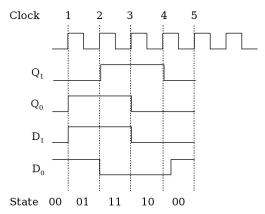

An example of a State Machine as a Generalized counter (38) is a Grey Code counter. Suppose we want to have 8 states is count 0-7. => Need 3 bit register. 1 Write a Truth Table for the register Dinputs and Q outputs Next {Di} Previous [Q;] ( input to combe logic) ( output of combe logic ) 92/0 Q, Qo D Dz 0 0 0 0 1 6 0 1 0 0 0 0 1 1 1 0 0 0 1 1 1 1 Ο 1 T 1 1 1 0 0 l 1 0 0 1 0 0 0 Ο 0 Now simply read-off minterms from table  $P_{o} = \overline{Q} \cdot \overline{Q}_{1} \cdot \overline{Q}_{2} + Q_{o} \cdot \overline{Q}_{1} \cdot \overline{Q}_{2} + \overline{Q}_{o} \cdot Q_{1} - Q_{2} + Q_{o} \cdot Q_{1} \cdot Q_{2}$  $\overline{\varphi_1} \cdot \overline{\varphi_2} + \varphi_1 \cdot \varphi_2$ Ξ  $q_o \cdot \overline{q},$ + 2. . 0.  $D_1 =$  $\langle$  $D_z =$ Q. Q, + Q. · Qz Qo  $Q_{|}$ Q2 Ø D Q Q D Q Q Q Ck

Note The trajectory of this state machine fills the entire space. If instead one made a divide-by-k, where k<2" then some states " would never be reached under normal operation - called excluded states,

one must take care, that if an excluded state is reached (21) (e.g. at power-up) then the comb" logic will insure that eventually a state within the trajectory will be reached.

example consider a down-counter following the sequence For  $3 \rightarrow 2 \rightarrow 1 \rightarrow 3$  ... ie (11)  $\rightarrow$  (10)  $\rightarrow$  (01)  $\rightarrow$  (11). Excluded state is (00). The truth table is

| Previous {Ois |    | Next SDis |    |    |         |                     |                                                                |               |

|---------------|----|-----------|----|----|---------|---------------------|----------------------------------------------------------------|---------------|

| Q             | Qo | D         | Do |    |         |                     |                                                                | _             |

| 1             | 1  | 1         | 0  |    | $D_0 =$ | $Q_{0} \cdot Q_{1}$ | $+ \overline{Q}_0 \cdot Q_1 = $ $+ Q_0 \cdot \overline{Q}_1 =$ | <i>Q</i> ₀⊕Q, |

| 1             | D  | 0         | ł  | => |         |                     |                                                                |               |

| 0             | l  | 1         | 1  |    | $D_1 =$ | ao · Q              | $+ q_0 \cdot Q_1 =$                                            | Q.            |

|               |    |           |    |    |         |                     |                                                                |               |

Note that if one uses  $D_0 = Q_0 \oplus Q_1$  then the excluded state  $(00) \rightarrow (00)!!$ ie if the circuit ever winds up in (00) it will stay there. A way to avoid this problem is to add minterms corresponding. i.e. let  $D_0 = Q_0 \cdot \overline{Q}_1 + \overline{Q}_0 \cdot Q_1 + \overline{Q}_0 \cdot \overline{Q}_1 + \overline{\overline{Q}_0 \cdot \overline{Q}_1}$

$$= (Q_0 + \overline{Q}_0) \cdot \overline{Q}_1 + (Q_1 + \overline{Q}_1) \cdot \overline{Q}_0 = \overline{Q}_0 + \overline{Q}_1 = \overline{Q}_0 \cdot \overline{Q}_1$$

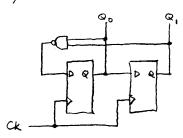

soy a circuit for the down- counter which doesn't get locked in (00) is

Phys 315/519

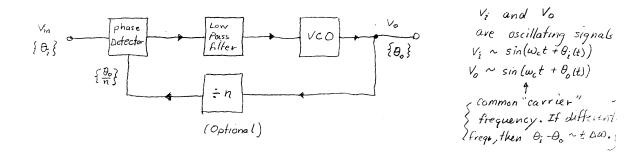

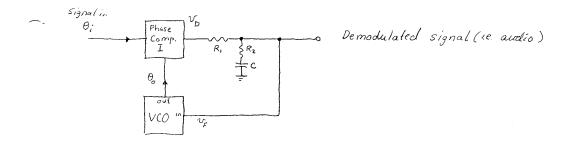

Phase Locked Loop

When we analyzed OPAMP feedback circuits recall that the "PAMP compared an input voltage vin to a feed back modified ression of its output voltage, Bvo. The operation was such as to reduce the error vin - Bvo to zero.

The Phase Locked Loop is also a feedback circuit but the quantity which is being compared is the phase of oscillatory signals. The basic topology looks like the following diagram.

The cutput of the phase detector is a voltage related to the difference in phases  $\theta_i - \frac{\theta_0}{n}$ . After fillering this voltage is applied to voltage controlled oscillator VCO to modify  $\theta_0$  to give a constant phase difference  $\theta_e = \theta_i - \frac{\theta_0}{n}$  at the phase detector.

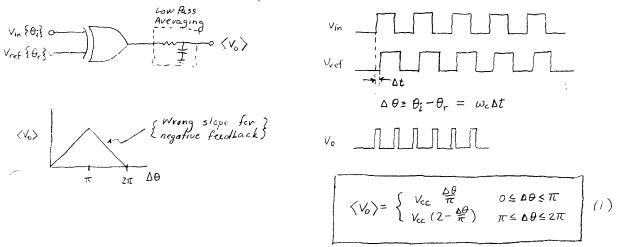

# Type I Phase Detector

1) XOR - Used w/ 50% duty factor square waves

Digital

(2)

5

- Note: i) if ref is at a harmonic or subharmonic of Vin then (Vo) is unchanged. Therefore PLL can lock onto harmonics of input frequency when using Type I detectors

- ii) Initially assume VCO is free running before input applied. Then  $\langle V_o \rangle = \frac{i}{2} V_{cc} \Rightarrow VCO$  will go to center frequency.

- iii) When loop is in lock the  $\Delta\theta$  corresponds to that needed to give the necessary VCO input voltage for the input trequency, ie if input freq near max of VCO's vange then  $\Delta\theta \rightarrow \pi$ .

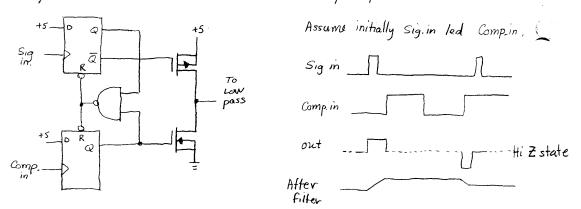

## Type I Phase Detector

Edge sensitive network - based on Flip-Flops

Advantages: Correction pulses generated only when needed. Doesn't lock on harmonics DO = 0 when locked - indep off

Disadvantage: sensitive to noise and distortion.

wiggle interpreted as two edges.

3

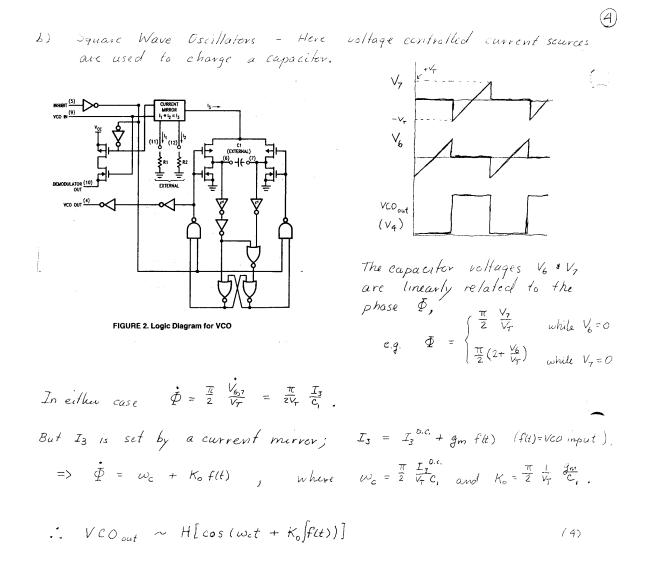

#### VCO and FM Generation

- Claim: suppose control voltage (ic audio) = f(t). Then output waveform

cos (wet + Sf(t)dt). Two examples;

- a) Sinusoidal Oscillators usually have an LC tank circuit in feedback loop, periodic pulse of current

The variable capacitance is most easily realized

arith a varactor - back biased didle whose junction

capacitarice depends on voltage.

$$\frac{1}{1} = \frac{1}{1} \frac$$

Considering the LC tank circuit above; I = CV = - IV or

$L C_0 (1 + \frac{\Delta C}{C_0}) \ddot{V} = V$  where  $\Delta C = change in capacitance due (1) to modula ting (audio) signal <math>\Delta V_B = f(t)$ .

Assume a solution of the form;  $V \sim e^{\frac{i}{p}\Phi(t)}$  where  $\Phi$  is assumed n to have primarily a linear dependence. In particular approximate  $\tilde{H}^* \Phi = 0$  n>1. (i.e. assume there are only smooth changes in  $\Phi$ )

Putting thus solution into (1)

$$\Rightarrow \quad \vec{p} = \frac{1}{\sqrt{LC_0(1+\frac{\Delta C}{2})}} \quad \simeq \quad \sqrt{LC_0} \quad (1-\frac{1}{2} \frac{\Delta C}{C_0}) = \omega_c + K_0 \quad f(t) \quad (2)$$

where  $\omega_c = \frac{1}{\sqrt{LC_0}}$  and  $K_0 = \frac{1}{4} \frac{\omega_c}{(V_3 + 0.6)}$ .

$(\frac{\omega_c}{2\pi} \quad called \quad the \ carrier \ frequency \ and \ K_0 \ is \ the \ VCO \ gain'' \ in \ \frac{r_{od}/scc}{V_0/t})$

iden

$$V \sim Re e^{\int p(t)} = \cos(\omega_{c}t + K_{o}\int f(t))$$

$$(K_{o}\int f(t)) \text{ is called the frequency duration})$$

$$(3)$$

Compare (3) to text sec 13.18.

### Phys 315/519

#### Digital

Here the so the Heavy side function - turns sine wave into square wave

Assume Signal input Vilt) ~ H[sin(wet + 0:4))]

and VCO cutput VCO out)~ H[cos(wct+0.(t))]

Note a 90° phase shift between input and VCO output is included explicitly since that phase difference corresponds to the mid value of the Type I phase comparator output.

hase Compoutput:

$$v_{\rm D} = K_{\rm D} (\theta_i - \theta_{\rm D})$$

Filter cutput :  $v_{\rm F} = K_{\rm F} v_{\rm D}$  where  $K_{\rm F} = \frac{1 + j\omega \tau_2}{1 + j\omega (\tau_1 + \tau_2)}$ ,  $\tau_{\rm n} = R_{\rm n}C$ .

VCO cutput :  $\theta_{\rm O} = K_{\rm O} v_{\rm F} => \theta_{\rm O} = \frac{1}{j\omega} K_{\rm O} v_{\rm F}$

(Note the  $\omega$  in above expressions relates to the time dependence of  $\theta_i \neq \theta_{\rm O}$ )

The loop equation is  $\theta_{\rm O} = \frac{1}{j\omega} K_{\rm O} K_{\rm F} K_{\rm D} (\theta_i - \theta_{\rm O})$ ,

$$= \rangle \qquad \theta_{0} = \frac{\frac{1}{j\omega} K_{0} K_{0} k_{F}}{1 + \frac{1}{j\omega} K_{0} K_{D} K_{F}} \quad \theta_{i} \qquad (5)$$

The resistors R, dR2 are usually chosen R2 << R, to give a Bode plot

$$\frac{1}{2} + \frac{1}{2} + \frac{1}$$

6)

Long the expression for KE, equation (5) becomes

$$\frac{G_o}{G_i} = \frac{K_o K_o (l + j \omega \tau_z)}{-\omega^2 (\tau_i + \tau_z) + j \omega (l + \tau_z K_o K_o) + K_o K_b}$$

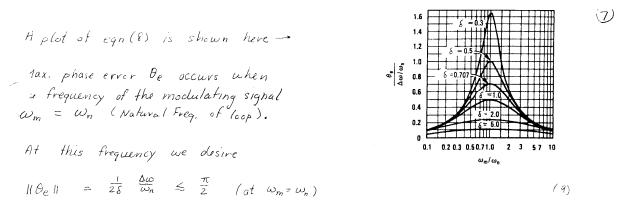

$$= \frac{1+j\omega\tau_{2}}{-\frac{\omega^{2}}{\omega_{n}^{2}}+2j\delta\frac{\omega}{\omega_{n}}+1} \qquad \text{where} \qquad \omega_{n} = \left[\frac{K_{o}K_{o}}{(\tau_{1}+\tau_{2})}\right]^{1/2} \quad (loop Natural Frequency)$$

$$anol \quad \delta = \frac{1}{2}\sqrt{(\tau_{1}+\tau_{2})K_{o}K_{b}} \quad (1+\tau_{2}K_{o}K_{b}) \quad (Damping Factor)$$

$$\sum_{nole} \delta \simeq \frac{1}{2}\omega_{n}\tau_{2} \quad \text{if} \quad \tau_{2}K_{o}K_{b} >>1$$

Since the PLL is to be used to demodulate FM the loop bandwidth  $\sim \omega_n$ should be made as large as possible in order to follow the signal. On the other hand it must not be excessively large to avoid noise. Since we're interested in audio we'll anticipate  $\omega_n \simeq 2\pi \times 20 \text{ kHz}$ .

Also in order for the loop to remain locked with input the phase ervor ( should be limited to £90°. (Otherwise may againe positive feedback of Consider sinusoidal FM; r immt <u>Dw</u> jumt

$\Theta_i^{(t)} = \Delta \omega \int e^{j\omega m t} dt = j\omega_m e^{j\omega_m t}$ , where  $\omega_m = modulahing$  frequency  $\Delta \omega = amplifude of freq, deviation.$

$$= \widetilde{\theta}_{i}(\omega) = \frac{\Delta \omega}{j \omega_{m}} \delta(\omega - \omega_{m}) \qquad (note: work \omega / Fourrur Transforms)$$

(7)

Using (6) and (7) the phase error can be approximated

$$\theta_{e} = \theta_{i} - \theta_{o} = \left(I - \frac{\theta_{o}}{\theta_{i}}\right) \theta_{i} \simeq \frac{-\left(\frac{\omega_{m}}{\omega_{n}}\right)^{2} \frac{\Delta \omega}{\omega_{m}}}{-\left(\frac{\omega_{m}}{\omega_{n}}\right)^{2} + 2j \delta \frac{\omega_{m}}{\omega_{n}} + 1} \qquad 0$$

$$\frac{\theta_e}{\Delta \omega / \omega_n} = \frac{j \frac{\omega_n}{\omega_n}}{1 - \left(\frac{\omega_m}{\omega_n}\right)^2 + 2j \delta \frac{\omega_n}{\omega_n}}$$

(8)

Equis (6) and (9) can be used to set the filter component values,

$$\underbrace{E_{X}}_{VCO} \underbrace{Dafa}_{i} K_{D} = \frac{V_{cc}}{\pi} = 1.59 \quad V/rod \quad for \quad V_{cc} = 5V$$

$$\underbrace{VCO}_{i} \underbrace{Dafa}_{i} \frac{VCO_{in}}{1.25V} \quad \frac{f}{33kH_{2}}$$

$$\underbrace{2.5V}_{i} 98 \quad kH_{2}}_{i} = K_{o} = \frac{2\pi (117 \ kH_{2})}{2.5V} \approx 3 \times 10^{5} \frac{rad/scc}{V}$$

Choose  $\omega_n \simeq 2\pi \times 10 \text{ Hz}$  for audio, then from egf (6)

$$T_1 + T_2 = \frac{K_0 K_0}{\omega_0^2} = 1.2 \times 10^{-4} \text{ sec}$$

A damping factor of 0.5 < S < 1 usually gives good performance i.e. not too much ringing. Usually S = 0.7 is considered optimum. Hiso from eq<sup>1</sup>(6)

$$\mathcal{T}_2 \simeq \frac{2S}{\omega_n} = 2.2 \times 10^{-5} \text{ sec}$$

An acceptable set of values would be  $R_1 = 9.1 k_{\Omega}$   $C_1 = 10 nf$  $R_2 = 2.2 k_{\Omega}$

Since  $\delta = .7$  the frequency deviation should be considered to (using eq 2.195)  $\Delta \omega \leq \pi \delta \omega_n = 1.2 \times 10^5 \text{ rad/sec}$  or  $\Delta f \simeq 20 \text{ kHz}$ For  $f_c = 100 \text{ kHz}$  (carrier) this represents a 20% modulation,

#### Data Conversion

The measurement of some physical property by an electronic transducen is usually an analog voltage or current which is related (1-to-1) to the value. Subsequently one wishes to either store the measured value or use it in a further computation. In either case it turns out to be most convenient to convert the measurement to a number - binary or otherwise.

# Digital to Analog Conversion (DAC)

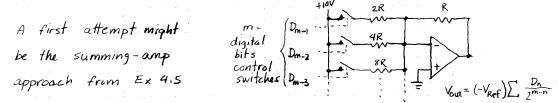

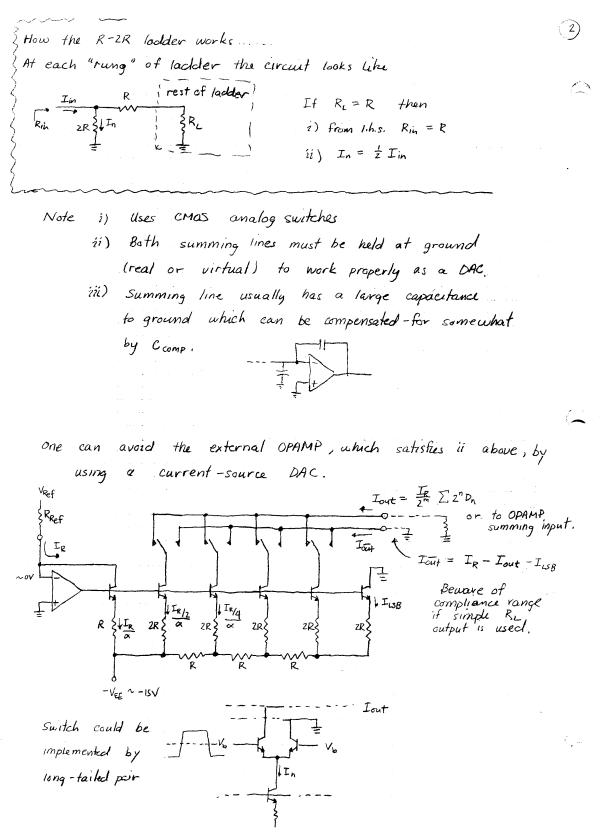

Begin first with the inverse operation: given a number convert it to a voltage or current. (This forms the basis of all feedback analog - to - Digital converters) It turns out, due to the KCL that digital conversion to current is the most natural.

The main disadvantage of this scheme is that an n-bit DAC would require n+1 different resistor values, each one having an absolute accurracy  $= \pm \text{ smallest value, ie for a 10-bit}$ converter the largest resistor would need 0.05% accuracy.

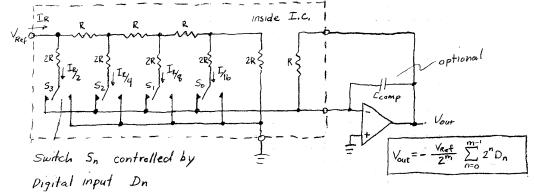

A more elegant scheme which uses only two resister values is the R-2R Ladder. A 4-bit version is shown below

## Phys 315/519

Digital

29

$$\frac{DRC}{Suppose} = \frac{\text{Error Specifications}}{\text{Suppose}}$$

Suppose a voltage output although same results up obvious modifications will apply to current out. I deally the valtage levels out should be related to digital code by  $V_{\text{out}} = V_{\text{REF}} \times \frac{1}{2}m \sum_{m=0}^{m-1} D_m \cdot 2^m$ .

Between adjacent numbers Vous should change by an amount corresponding to the least-significant bit, is  $\Delta V_{\text{out}} = \frac{V_{\text{REF}}}{2} = \frac{V_{\text{LSF}}}{2}$ .

Also note that minVout = 0 and max Vout =  $V_{\text{REF}} - V_{\text{LSB}} = \frac{V_{\text{LSF}}}{2}$ .

(is maw Vous New =  $\frac{1}{2}m \sum_{j=1}^{m-1} 2^m = \frac{1}{2}m \left(\frac{j-2}{2}\right) = 1 - \frac{1}{2}m$ ).

Consider transfer curve Vout vs digital code

$V_{\text{ES}} = \frac{1}{\sqrt{16}} \sum_{j=1}^{m-1} \frac{1}{$

4) Monstonicity

~

companisons

- i) The current mode DAC is unipolar in IR>0 required, while analog switch DAC is bipolar in Vref \$0 (IR\$0) allowed.

- ii) although both DACs require only two resistor values the current mode DAC must have in different sized transistors so that  $I_s$  (from Ebers Moll) scales. This is needed to insure all ladder transistors have same  $V_{BE}$ , since  $\Delta V_{BE} \sim 60 \text{mV}$  for  $\frac{T}{T_z} = 10$ .

- iii) Current-mode DAC output capacitance ~ constant while analog-switch DAC capacitance varies w/ code. Only affects high speed operation.

- iv) As presented both DAC are "multiplying" is Vout & Vref. Some analog-switch DACs have Vref and output amplifier integrated.

26

S Analog to Digital Conversion Given a voltage range defined by limits VRT + VRB where VRT > VRB. Divide the range into 2<sup>m</sup> equal intervals having boundaries  $V_{k} = V_{RB} + (V_{RT} - V_{RB}) \frac{k}{2^{m}}$ ,  $k = 91, \dots, 2^{m} - 1$ . The task of the ADC is to find k such that Vk < Vin < Vk+1 There are two broad categories; sampling (converts Vin (tmas, 1) and integrating (converts (Vin>). Examples of each are given below 1. Parallel Encoding ("Flash" ADC) Conceptually simple but requires lots of circuitry e.g. 2 comparators! VRT -Comparator An example of a 3-bit Flash ADC RŚ is shown to left. If  $V_k < V_{in} < V_{k+1}$ then  $C_p$  output is {0 if 2 > k1 if 2 < k. R R The priority encoder gives the 民子 3-bit address of the highest  $-A_z$  $-A_1$  $-A_0$ RŚ numbered comparator which R was on. R R Priority Encoder VRB Vin Register CONV

> Note that the Register plays the role of a digital sill t; when conv is the comparator outputs are latched. and Vin may change without affecting the conversion,

This is the fastest method of A-D conversion however typically it is limited to lower resolution (less bits) than other methods due to large amount of circuitry.

Also comparator Vos must be < Im (VRT-VRB) to avoid nonlinearity.

$\sum_{i=1}^{n}$

(

i i

one can greatly reduce the number of Comparators etc needed (4) with the addition of a DAC in the following feedback methods

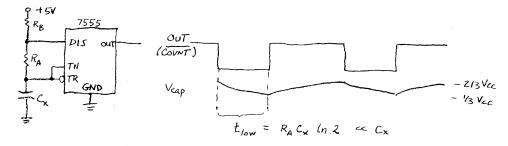

2. Tracking ADC  $\begin{array}{c} c_{k} & \downarrow \downarrow c_{in} & \downarrow 469 \\ \hline U_{0} & \hline U$

This scheme is slow; the max  $\frac{dV_{in}}{dt}$  that can be followed is  $V_{LSB} * f_{ck}$ . If Vin changes faster than this then one should use a S&H in front of comparator and wait 256 (2<sup>m</sup>) clock cycles.

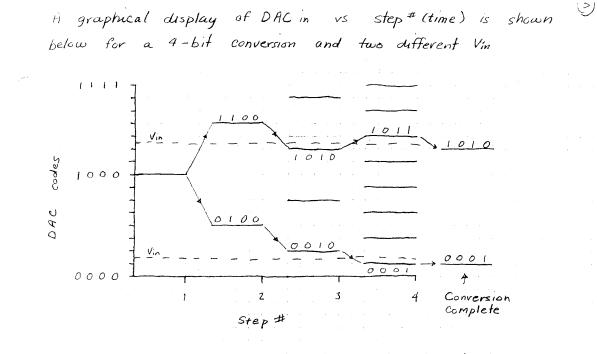

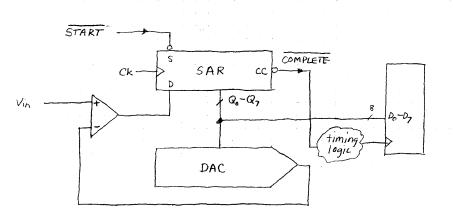

3. Successive Approximation

This method iteratively bisects the voltage range to find the binary # of the interval containing Vin. At each iteration the range is reduced by 2. For m bits the answer is arrived at in m steps (rather than 2<sup>m</sup> as above).

Stepl: Set DAC MSB=1, all others = 0 ie. 100... =) VDAC = 1/2 F.S.

- Step 2: if Vin > Vonc leave MSB=1 Vin < Vonc set MSB=0 / This redefines the range to be the upper or lower half of the original range. Then set bit MSB-1 = 1 and all lesser bits = 0. => VOAC = { <sup>3</sup>4 F.S. if 1100.... <sup>1</sup>4 F.S. if 0100....

- Step 3: Test  $V_m \leq V_{DAC}$  as above and adjust bit MSB-1. Then set bit MSB-2 =1 and all lesser bits = 0. etc.....

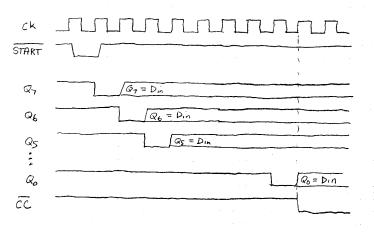

The sequential logic which does this is called a "Successive-Approximation Register" or SAR. Its use in an ADC is shown below.

It is crucial that Vin remain constant within 1/2 LSB during the conversion. If this isn't the case then the comparator Vin input should be preceeded by a S&H

The SAR we use in Lab (\*LS503) assumes neg-true logic on its I/O pins although it isn't obvious from the data sheet diagram. The LS503 assumes that a  $\underline{o}$  data output <u>adds</u> current to the DAC output, ie 000...=>FS. and III...=>  $v_{bac}=0$ . One can nevertheless hook it up as shown on prev. pg or in lab manual and it will work, but there will be a few missing codes even if DAC is perfect. Doing it correctly involves swapping +/- inputs of comparator and adding inverters between SAR outputs and DAC inputs, or using complementory current output if there is one.

Given the Ck and S inputs as shown the outputs are

Since both  $Q_0$  and  $\overline{CC}$  change in response to Ck fyou would want to latch output data when Ck fand  $\overline{CC} = 0$ , ie

$$\frac{Ck}{CL} = \frac{1}{2}$$

The linearity of the Tracking and SAR ADCS depends directly on the quality of the DAC, if it is nonlinear then the ADC will exhibit the same type of nonlinearity. In the following ADCs Vin is converted into a pulse whose duration is measured with a stable clock and counter, avoiding the necessity of a DAC altogether.

Digital

$\checkmark$

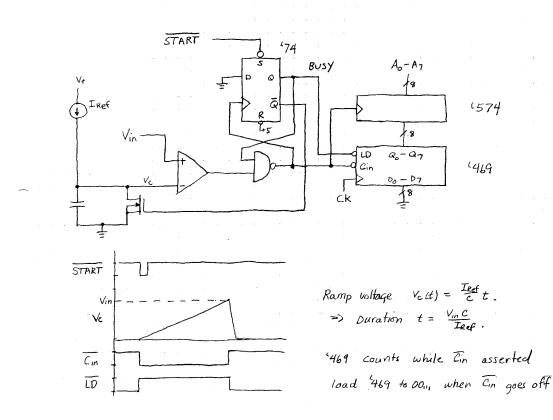

4. Single Slope Converter

When done, the count  $m = f_{clock} t_{ramp} = \frac{f_{clock} c}{I_{Ref}} \times V_{in}$

I scale errors if C, IREF or felock drift w/ time # temp.

However it is monotonic and DNL is good since any drift usually occurs on a much longer time scale than tramp.

Any variation of Vin (e.g. noise spikes) occuring near end of ramp

will cause error.

9

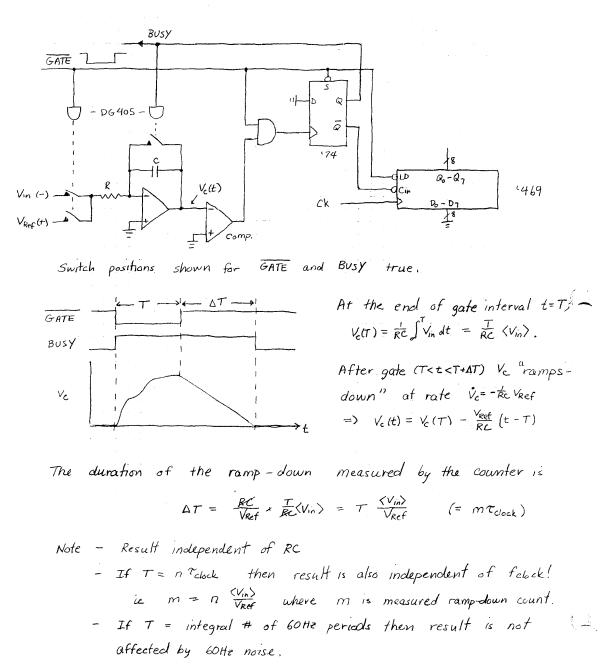

5. Dual Slope Converter

By averaging input this method is less sensitive to noise on Vin, and even becomes independent of R, C and perhaps flock.

of the various "slow" methods this one is the best in most cases.

、ワ

Other integrating converters ....

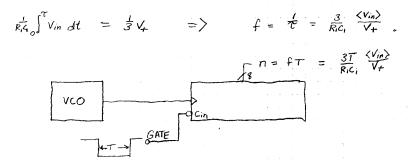

7. VFC (Voltage - to-Frequency)

This method counts the number of cycles of a voltage controlled oscillator accuring during a fixed time interval, say isec. Recall the VCO analyzed in Ex 4.13 on pg 240 of  $H^2$ . Each cycle of the output waveform required a time  $\tau$  given by

8. Delta-Sigma converter

This is similar to the VFC except that neg feedback is use to insure a linear VCO.