# VME64 Extensions for Physics and Other Applications (VME64xP)

VITA 23-199x Draft 1.3 10 December 1997

## Implementation Rules, Recommendations & Guidelines

This document has been prepared by the VME International Physics Association (VIPA) under the

VITA Standards Organization (VSO)

7825 East Gelding Drive, Suite 104

Scottsdale, AZ 85260

Phone: (602) 951-8866 FAX: (602) 951-0720

This document is not an approved VITA or VIPA document.

Do not specify or claim conformance to this document.

#### Foreword

This document is intended to be used internationally in physics applications and in other fields with similar requirements. The original VMEbus standard was sponsored by the Technical Committee on Microprocessors and Microcomputers of the IEEE Computer Society. It was approved by the IEEE and the American National Standards Institute (ANSI) and issued by the IEEE as ANSI/IEEE Std 1014-1987. The VME64 Standard, ANSI/VITA-1-1994, was developed in 1994 by the VME International Trade Association (VITA) and processed through the American National Standards Institute (ANSI) by the VITA Standards Organization (VSO). It is based on the VMEbus bus specification released in August 1982 by the VMEbus Manufacturers Group (now VITA). A complete chronology appears in the Foreword of the VME64 Standard, ANSI/VITA 1-1994. The VME64x draft standard VITA 1.1-199x is nearing approval.

VIPA (VITA International Physics Association) is a VITA Special Interest (User) Group that represents the international physics community in VSO. VIPA was formed to make the VSO aware of the needs of the physics research community. VIPA is also interested in achieving increased standardization in VMEbus implementations in the physics community worldwide.

VIPA has membership in VITA through the Fermi National Accelerator Laboratory in Batavia, Illinois, USA, the European Organization for Nuclear Research (CERN) in Geneva, Switzerland, and the JVP Working Group in Japan. The VIPA membership consists of:

- NIM VME-P Working Group: The NIM VME-P working group is the entity under the NIM (Nuclear Instrumentation Module) Committee that is concerned with VME for physics applications in North America. NIM refers to the U. S. Department of Energy Committee that developed the NIM modular instrumentation system (DOE/ER-0457T and IEC Standard 547) and collaborated with ESONE in the development of FASTBUS (ANSI/IEEE Std 960 and IEC Standard 935) and CAMAC (EUR-4100, IEEE Std 583, IEC Standard 516) bus systems.

- VMEbus Steering Committee: The VMEbus Steering Committee (VSC) is a Study Group of ESONE, the committee for European Studies On Norms for Electronics. One of ESONE's aims is to promote the use of standards in research in Europe and to collaborate in the development of standards where none exist. ESONE developed CAMAC, an early modular bussed digital instrumentation system, in collaboration with NIM. More recently it developed VICbus (ISO/IEC 11458) and produced its own set of recommended practices for the use of VMEbus in Physics before joining forces with the NIM VME-P committee within VIPA. A subset of the VSC also functions as an internal advisory committee on VMEbus at CERN, the European Laboratory for Particle Physics.

- JVP Working Group: JVP is the Japanese VME Physics working group concerned with VME for physics applications.

The VMEbus standards are the basis for this document. Hardware and software produced according to this document will be in full compliance with the VMEbus standards. The Rules, Recommendations, Observations, *etc.* in this document are complementary to and compliant with existing VME standards. The Rules in this document are based on either Rules, Recommendations or Suggestions in a VME standard or draft standard as well as items not addressed by VME standards.

This document is generally consistent with the NIM/VME-P document 9612, "VMEbus for Physics Applications", that has served as a working group approach, and has also utilized items from the CERN VSC "Recommended Practices" document.

The involvement of VIPA in the VME International Trade Association (VITA), besides resulting in this document, has also beneficially influenced the VME Extensions draft standard to better meet needs of the physics community as well as those of the entire VME users community. This is reflected in many of the items in the VME64 Extensions standard (VITA 1.1-199x). Additionally, the VME64x 9U x 400 mm Format draft standard (VITA 1.3-199x) has been largely produced by VIPA representatives who have also contributed substantially to (IEEE) P1101.11 (Mechanical Rear Plug-in-Unit Specifications for Microcomputers using IEEE 1101.1 Equipment Practice).

## Editors (to whom comments and inquiries can be addressed):

Edward J. Barsotti Fermilab, MS 222 P.O. Box 500 Batavia, IL 60510 USA

E-mail: barsotti@fnal.gov Phone: + 1 630 840 4061 FAX: +1 630 840 5406

Robert W. Downing Fermi VSO Representative 1067 Bucks Pond Rd. Monticello, IL USA E-mail: rwd@uiuc.edu Phone: +1 217 762 4401

FAX: +1 217 762 3029

Louis Costrell

National Institute of Standards & Technology

Ionizing Radiation Division

Gaithersburg, MD 20899 USA

E-mail: costrell@nist.gov

Phone: +1 301 975 5608

Phone: +1 301 975 5608 FAX: +1 301 869 7682 Christopher Parkman ECP Division CERN

CH - 1211 Geneva 23 SWITZERLAND E-mail parkman@cern.ch Phone: +41 22 767 3963 FAX: +41 22 767 5490

Hirofumi Fujii

National Laboratory for High Energy Physics, KEK

Physics Division

Oho 101, Tsukuba Ibaraki 305 Japan

E-mail: hirofumi.fujii@ kek.jp

Phone: +81 298 64 5381

FAX: +81 298 64 3136

Michael Harms

Stanford Linear Accelerator Center

2575 Sand Hill Rd.

P. O. Box 4349

Stanford, CA 94309 USA

E-mail: harms@slac.stanford.edu

Phone: +1 650 926 2915

Fax: +1 650 926 3800

## **Acknowledgments:**

In addition to the editors and working group chairs, persons who have been responsible for producing various sections of this document or who have made significant contributions include:

John Anderson, Fermilab Jan Buytaert, CERN Michael Chorowicz, CES Richard Hance, Fermilab Bill W. Haynes, Fermilab John Hoftiezer, Ohio State University James Pangburn, Fermilab Ludwig Pregernig, CERN Uwe Uhmeyer, LeCroy Eike Waltz, Rittal

## VITA 23-199x Task Group Members

John Anderson, Fermilab

Edward Barsotti, Fermilab

Janos Biri, BFKI-MSZKI

George Blanar, LeCroy

Mark Bowden, Fermilab

Jan Buytaert, CERN

Gorky Chin, VISTA Controls

Louis Costrell, NIST

Bob DeMaat, Fermilab

Robert Downing, Consultant

Philippe Farthouat, CERN

Wayne Fischer, Force Computers

Lou Francz, Dialogic

Jim Fowlie, Pentland Systems

Richard Hance, Fermilab

Michael Haney, University of Illinois

Michael Harms, SLAC

Bill W.Haynes, Fermilab

John Hoftiezer, Ohio State University

Frank Hom, Electronic Solutions

Wolfgang Khuen, WES-Crates

Tad Kubic, Dawn

Tony Lavely, Mercury Computer Systems

Andreas Lenkisch, TreNew

Martin Merkel, CERN

Tim Morrow, Westinghouse Electric

Michael Munroe, ERNI

Dieter Notz, DESY

Tokio Ohska, KEK

James Pangburn, Fermilab

Christopher Parkman, CERN

Elwood Parsons, AMP

Robert Patterson, AMP

Manfred Pernicka, Inst. für Hochenergy Physik

Ruth Pordes, Fermilab

Ludwig Pregernig, CERN

Raymond Rausch, CERN

Dave Robak, Harting

John Rynearson, VITA

Richard Schweitzer, CERN

Theresa Shaw, Fermilab

Holly Sherfinski, Harting

Morton Thayer, C-MAC

Michael Thompson, Schroff

Uwe Uhmeyer, LeCroy

Jean-Pierre Vanuxem, CERN

Eike Waltz, Rittal

Kerry Woodbury, Fermilab

David Wright, Hybricon

## VME International Physics Association (VIPA) Constituents:

NIM VME-P Working Group ESONE VSC (VME Steering Committee) JVP (Japanese VME Physics) Working Group

## NIM VME-P Working Group

Chairman: Edward J. Barsotti

John T. Anderson Gunther Haller Hari Areti Richard D. Hance Christopher Bebek Michael Harms Chi Cheng-Yi Bill W. Havnes David F. Conner John Hoftiezer Louis Costrell Thomas Kozlowski David C. Doughty Edward J. Lampo Robert W. Downing Raymond S. Larsen John Elias Ronald O. Nelson Allan Gjovig Leo Paffrath Robert Goodwin James Pangburn **Ruth Pordes** John S. Haggerty

Theresa Shaw Robert Scheets Keith Schuh Michael F. Shea William P. Sims Mathew Stettler Mike Thompson Uwe Uhmeyer Graham Waters Kerry Woodbury

## ESONE VSC (VME Steering Committee)

Chairman: Christopher Parkman

Jan BuytaertMartin MerkelRaymond RauschMichel ChorowiczChris ParkmanRichard SchweitzerPhilippe FarthouatLudwig PregernigJean-Pierre Vanuxem

## JVP (Japanese VME Physics) Working Group

Chairman: Hirofumi Fujii Vice-Chairman: Masaharu Nomachi

Hirofumi Fujii Osamu Sasaki Tokio K. Ohska Yoshiji Yasu

## TABLE OF CONTENTS

## **CHAPTERS**

| 1. INTRODUCTION                                                      | 1-1 |

|----------------------------------------------------------------------|-----|

| 1.1. GENERAL INFORMATION                                             | 1-1 |

| 1.2. REFERENCE SPECIFICATIONS                                        | 1-2 |

| 1.3. COMPLIANCE WITH VMEBUS STANDARDS AND COMPATIBILITY ISSUES       | 1-2 |

| 1.4. CHAPTER AND APPENDIX CONTENT SUMMARIES                          | 1-3 |

| 1.4.1. Body                                                          | 1-3 |

| 1.4.2. Appendices                                                    |     |

| 1.5. VMEBUS OVERVIEW                                                 | 1-4 |

| 1.5.1. Address Space                                                 | 1-4 |

| 1.5.2. Data Transfer Cycles                                          | 1-5 |

| 1.6. VME64 Extensions                                                | 1-6 |

| 1.7. VME64xP Features                                                | 1-6 |

| 1.7.1. VME64xP Modules, Transition Modules, Power Transition Modules | 1-7 |

| 1.7.2. VME64xP Subrack                                               | 1-8 |

| 1.8. Software                                                        | 1-9 |

| 2. INTERPRETATIONS, DEFINITIONS, ACRONYMS & REFERENCES               | 2-1 |

| 2.1. Interpretation of this Document                                 | 2-1 |

| 2.2. NOTATIONS AND LOGIC SIGNAL CONVENTIONS                          | 2-2 |

| 2.3. Definitions                                                     | 2-2 |

| 2.3.1. VME64xP Definitions                                           | 2-2 |

| 2.3.2. Other Definitions                                             | 2-3 |

| 2.3.3. Acronyms                                                      | 2-3 |

| 2.4. Other References                                                |     |

| 3. ADDRESS MODES, DATA WIDTHS, AND CR/CSR DEFINITIONS                | 3-1 |

| 3.1 Introduction                                                     | 3-1 |

| 3.2 ADDITIONAL ADDRESSING & DATA WIDTH REQUIREMENTS                  |     |

| 3.3 ACCESSING CR/CSR REGISTERS & ADDITIONAL CR/CSR REQUIREMENTS      | 3-2 |

| 3.3.1 Base Address Register                                          | 3-2 |

| 3.3.2 Control Registers                                              | 3-3 |

| 3.3.3 VME64xP Control/Status Registers                               |     |

| 3.4 VARIABLE-LENGTH READOUT                                          | 3-6 |

| 4. VME64XP MODULES AND TRANSITION MODULES                            | 4-1 |

| 4.1 Introduction                                                     | 4-1 |

| 4.2 GENERAL SPECIFICATIONS                                           | 4-1 |

| 4.3 VME64xP Modules                                                  | 4-3 |

| 4.4 VME64xP Transition Modules                                       | 4-4 |

| 4.5 VME64xP MODULE AND TRANSITION MODULE DIE AND BOARD TEMPERATURES  | 4-6 |

| 4.6 VME64xP Module and Transition Module Circuit Protection          | 4-6 |

| 4.7 VME64xP Power Transition Modules                                 | 4-7 |

| 4.7.1 Input and Output Power for PTMs                                |     |

| 4.7.2 Power Code Pins for PTMs                                       |     |

| 5. MEZZANINE CARDS AND CARRIERS                                      | 5-1 |

| 5.1 Introduction                                                     | 5-1 |

| 5.2 PMC AND IP-MODULES                                               | 5_1 |

| 6. VME64XP SUBRACKS                                           | 6-1  |

|---------------------------------------------------------------|------|

| 6.1 Introduction                                              | 6-1  |

| 6.2 GENERAL SUBRACK MECHANICAL SPECIFICATIONS                 | 6-1  |

| 6.3 VME64xP Subrack Backplanes                                | 6-2  |

| 6.3.1 Connectors                                              | 6-3  |

| 6.3.2 J0 Connector Pin Assignments for VME64xP Backplanes     | 6-5  |

| 6.3.3 Terminated Bus Lines - TBUS                             |      |

| 6.3.4 Backplane Daisy Chain Jumpers                           | 6-8  |

| 6.3.5 Voltage, Temperature and Other Backplane Specifications | 6-8  |

| 6.4 TRANSITION MODULE CARD CAGE                               |      |

| 6.5 SUBRACK POWER CONNECTIONS                                 | 6-10 |

| 6.6 REMOTE SENSE AND MONITORING                               | 6-12 |

| 6.7 Subrack Cooling                                           | 6-12 |

| 7. POWER FOR SUBRACKS, MODULES AND TRANSITION MODULES         | 7-1  |

| 7.1 General                                                   | 7-1  |

| 7.2 VME64xP Power                                             |      |

## **APPENDICES**

| A. TYPE A-7U SUBRACK FOR 6U MODULES                                          | A-1  |

|------------------------------------------------------------------------------|------|

| A.1 Introduction                                                             | A-1  |

| A.2 SPECIFICATIONS FOR 6U MODULE SUBRACKS                                    |      |

| A.3 VIPA SUBRACK MODULE CARD CAGE                                            | A-2  |

| A.4 VIPA SUBRACK BACKPLANE                                                   |      |

| A.5 VIPA SUBRACK TRANSITION MODULE CARD CAGE                                 |      |

| A.6 VIPA SUBRACK POWER CONNECTIONS                                           |      |

| A.7 PSAB AND CONNECTIONS FROM BACKPLANE TO PSAB                              |      |

| A.8 CONNECTIONS FROM POWER SUPPLIES TO PSAB                                  |      |

| A.9 REMOTE SENSE AND MONITORING                                              |      |

| A.10 VIPA SUBRACK COOLING                                                    | A-10 |

| B. TYPE A-10U SUBRACK FOR 9U MODULES                                         | B-1  |

| B.1 Introduction                                                             | B-1  |

| B.2 SPECIFICATIONS FOR 9U MODULE SUBRACKS                                    |      |

| B.3 VIPA SUBRACK MODULE CARD CAGE                                            |      |

| B.4 VIPA SUBRACK BACKPLANE                                                   |      |

| B.5 VIPA SUBRACK TRANSITION MODULE CARD CAGE                                 | B-6  |

| B.6 VIPA SUBRACK POWER CONNECTIONS                                           | B-6  |

| B.7 PSAB AND CONNECTIONS FROM BACKPLANE TO PSAB                              | B-8  |

| B.8 CONNECTIONS FROM POWER SUPPLIES TO PSAB                                  | B-9  |

| B.9 REMOTE SENSE AND MONITORING.                                             | B-9  |

| B.10 VIPA SUBRACK COOLING                                                    | B-11 |

| C. KEYING FOR SUBRACKS, MODULES, AND TRANSITION MODULES                      | C-1  |

| C.1 Introduction                                                             |      |

| C.2 GENERAL REASONS FOR KEYING                                               |      |

| C.3 SPECIFIC REASONS FOR KEYING - INFORMATION IN DEVICE SPECIFICATIONS       |      |

| C.4 Subrack, Module & Transition Module Keying Hole Positions & Keying Codes |      |

| C.5 KEYING RECOMMENDATIONS                                                   |      |

| C.6 How To Key A System                                                      | C-4  |

| D. TYPICAL VMEBUS SUBRACK POWER SUPPLIES                                     | D-1  |

| D.1 HIGH-EFFICIENCY, RACK MOUNTED POWER SUPPLY (TYPE HERM)                   |      |

| D.2 LOW-NOISE, RACK MOUNTED POWER SUPPLY (TYPE LNRM)                         |      |

| D.3 HIGH-EFFICIENCY, BACK MOUNTED POWER SUPPLY (TYPE HEBM)                   |      |

| D 4 LOW-NOISE BACK MOUNTED POWER SUPPLY (TYPE LNBM)                          | D-5  |

| E. CHAINED BLOCK TRANSFERS (CBLT) AND MULTICAST COMMANDS (MCSTART) | r) <b>E-1</b> |

|--------------------------------------------------------------------|---------------|

| E.1 Introduction.                                                  | E-1           |

| E.1.1 Chained Block Transfer (CBLT)                                | E-1           |

| E.1.2 Multicast Commands (MCST)                                    | E-1           |

| E.2 CYCLE IDENTIFICATION                                           | E-1           |

| E.2.1 CBLT                                                         | E-1           |

| E.2.2 MCST                                                         |               |

| E.3 Token Mechanism                                                |               |

| E.3.1 Position.                                                    |               |

| E.3.2 Mixing CBLT/MCST and Conventional Slaves                     |               |

| E.4 CBLT/MCST Protocols                                            | E-4           |

| E.4.1 D32 Transactions                                             | E-4           |

| E.4.1.1 CBLT                                                       |               |

| E.4.1.2 MCST                                                       |               |

| E.4.2 D64 (MBLT) Readout                                           |               |

| E.4.3 End of CBLT/MCST Transactions                                |               |

| E.4.4 Multiple CBLT Transactions                                   |               |

| E.4.5 Performance Optimization                                     |               |

| E.5 Data Frame                                                     |               |

| E.5.1 Data Frame Field Assignments                                 |               |

| E.6 EMPTY Modules                                                  |               |

| E.7 CR & CSR SPACE REQUIREMENTS                                    |               |

| E.8 TIMING SPECIFICATIONS                                          | E-12          |

9-Dec-97

This page intentionally left blank

## 1. Introduction

### 1.1. General Information

The VMEbus system is used in many areas of industry and science resulting in the manufacture of a wide variety of devices, including processors, by numerous companies with large volume production. For that reason it is attractive to and is used by the physics community though the original VMEbus had certain problems when used in research applications. For example, noise as a result of the shortage of ground pins, is a problem with sensitive analog circuits. Because VMEbus supports a wide variety of options, incompatibilities would sometimes arise in systems with modules that did not support the appropriate subset of options. The VME64 Extensions draft standard, VITA1.1-199x, has enhanced the VMEbus, mitigated many of these issues, and has generated interest in the wider use of VMEbus in physics research applications.

This document has been produced to supplement VMEbus specifications, particularly the VME64 specification (ANSI/VITA 1-1994) and the VME64 Extensions draft standard (VITA 1.1-199x), and to provide for the needs of the physics community and other users with similar requirements.

Readers of this document who have interest in a limited number of the Chapters and Appendices herein, will find summaries in Section 1.4.

The VME64 specification, ANSI/VITA 1-1994, establishes a framework for 8, 16, 32, and 64-bit parallel bus computer architectures that can implement single processor and multiprocessor systems. The VITA Standards Organization (VSO) has developed the VME64x draft standard. VIPA actively participates in VSO activities and provides considerable input as a result of which VMEbus is becoming even more attractive for physics applications. *VME64 Extensions for Physics*, VME64xP, builds on VME64 and VME64x and orients their use for physics and other fields with similar requirements. The following items are typical of the issues important to electronic systems used in research and are addressed in this document:

- Grounding

- High-frequency signaling

- Low noise for high-resolution analog signals

- User defined I/O pins

- Sparse data readout

- Geographical addressing

- Additional power supply voltages

- DC-DC on-board converters

- Efficient block transfer protocols

- Provision for cooling

- Standard Control and Status Registers (CSR)

- Data space addressing rules

- Design guides

## 1.2. Reference Specifications

The following documents are referenced herein and are necessary for a complete understanding of this document. (All IEC documents have the new numbering system which adds 60000 to previous numbers.)

• VITA 1-1994: ANSI/VITA 1-1994, VME64 Specification

• VITA 1.1-199x VME64 Extensions Draft Specification, (VME64x)

• VITA 1.2-199x: High Availability VMEbus Draft Specification

• VITA 1.3-199x: VME64x 9U x 400 mm Format Draft Specification (VME64x9U)

• VITA 1.4-199x: VME64x Live Insertion Draft Specification (VME64xLI)

VITA 2-199x: ETL Specification, Draft 0.4a, 2 April 1993

IEEE 1014: Versatile Backplane Bus (VMEbus) 1987

• IEEE 1101.1: IEEE Standard for Mechanical Core Specifications for Microcomputers using

IEC 60603-2 Connectors, 26 September 1991

• IEEE 1101.10: IEEE Standard for additional Mechanical Specifications for Microcomputers

using the IEEE 1101.1 Equipment Practice

• (IEEE) P1101.11: IEEE Proposed Standard for Mechanical Rear Plug-in Unit Specifications for

Microcomputers using the IEEE 1101.1 and IEEE 1101.10 Equipment

Practice

• IEC 60821: International Electrotechnical Commission equivalent of IEEE 1014

Other standards referred to herein are:

• IEC 60176-4: Connectors with Assessed Quality, for use in DC Low Frequency Analog and in

High Speed Data Applications - Part 4: Sectional Specification - Printed Circuit

Connectors

• IEC 60603-2: Connectors for Frequencies below 3 MHz for use with Printed Circuit Boards -

Part 2: Detailed Specification for Two-Part Connectors with Assessed Quality, for Printed Circuit Boards, for Basic Grid of 2.54 mm (0.1 in) with Common

Mounting Features

• IEC 60297-1: Dimensions of Mechanical Structures of the 482.6 mm (19 in) Series - Part 1:

Panels and Racks

• EIA 310-D: Cabinets, Rack Panels, and Associated Equipment

## 1.3. Compliance with VMEbus Standards and Compatibility Issues

Rules and Observations are defined in Section 2.1.

#### Rule 1.3-a (VME64xP compliance)

VME64xP Modules, Transition Modules and Subracks and the VME64xP protocols shall comply with the VME64 (ANSI/VITA 1) and the VME64 Extensions (VITA 1.1-199x) specifications.

#### **Observation 1.3-b (backward compatibility)**

The requirement of Rule 1.3-a is consistent with "backward compatibility" that the VMEbus Standards Organization mandates for VME standards such that new VMEbus systems may take advantage of new features or protocols but are encouraged to comply with all previous versions of the standard(s).

#### Observation 1.3-c (VME64xP specifications)

Some Recommendations in the VME64 Extensions are made Rules in this document to enhance compatibility between VME64xP Modules while adhering to the requirements of VME64 Extensions. Also included are other Recommendations, Observations, Permissions and Suggestions for designers of VME64xP Modules.

## **Observation 1.3-d (compatibility considerations)**

Though backward compatibility is obtained to a high degree in VMEbus systems, problems can be encountered (particularly with secondary P2/J2 buses) that require vigilance on the part of the system integrator in configuring the system. VME64xP Modules have the same compatibility problems when connecting to the user defined pins in P0/J0 and P2/J2. Careful and conscientious use of the optional keying feature can help prevent incompatible boards from being inserted into an "incorrect" slot.

## 1.4. Chapter and Appendix Content Summaries

This document has two distinct parts; the Body and the Appendices. The following summaries offer a descriptive outline of this document.

## 1.4.1. Body

The Body contains Rules which a VMEbus Module has to comply with to be called a VME64xP Module.

<u>Chapters 1 and 2</u> (Introduction and Interpretations, Definitions, Acronyms and References) These chapters contain introductory and explanatory items that are essential for proper understanding of this document.

<u>Chapter 3 (Address Modes, Data Widths, and CR/CSR Definitions)</u> This chapter summarizes the various addressing and data transfer protocols that have been developed as VMEbus standards. The chapter is concerned with addressing, Configuration ROM (CR), and Control/Status Registers (CSRs) for Modules.

<u>Chapter 4 (VME64xP Modules and Transition Modules)</u> This chapter includes construction details for Module and Transition Module manufacturers and points out the availability or non-availability of voltages that Module and Transition Module designers need to take into consideration. It also includes requirements for Power Transition Modules.

<u>Chapter 5 (Mezzanine Cards and Carriers)</u> This chapter deals with mezzanine cards which are circuit boards that mount in a Module parallel to the Module circuit board and are connected electrically to the Module circuit board. PMC and IP Module carriers are also briefly discussed.

Chapter 6 (VME64xP Subracks) This chapter describes two basic sizes of subracks, one for use with 9U x 400 mm Modules and the other for use with 6U x 160 mm Modules. The subracks include card cages for Transition Modules. The subracks defined are in full compliance with the VME64, VME64x (VITA 1.1-199x) draft standard and VME64x 9U x 400 mm (VITA 1.3-199x) draft standard but include or emphasize additional items. Of particular note are the backplane requirements and options as well as power connection details for several kilowatts of power. Also of note are the pin assignment table for the optional J0 connector and a discussion of the user-defined voltages that utilize that connector. Construction details, remote voltage sensing, and cooling considerations are also included. This chapter is also concerned with the accommodation of Transition Modules and their mating to the backplane. Examples of purchase specifications for typical subracks in compliance with this chapter are given in Appendices A and B.

<u>Chapter 7 (Power for VME64xP Subracks, Modules and Transition Modules)</u> This chapter deals with the voltages on the subrack backplanes and with the use of DC-DC converters mounted on the Module or Transition Module circuit board. It describes user defined voltages that utilize the optional J0 connector. (Specifications for typical rack-mounted and rear-mounted power supplies are included in Appendix D).

## 1.4.2. Appendices

The Appendices provide the user and manufacturer with specifications for VMEbus hardware which has wide usage in the Physics Research environment. This hardware is not required when implementing the body of this standard. However, if wide usage occurs, these Appendices can take on a "de facto standard" status. Unless there are conflicting system issues, the implementers can take advantage of the hardware described in these appendices to provide an increased degree of standardization and compatibility. The saving in time, money and the avoidance of errors in design are to the designer's advantage. In addition, the Appendices have suggestions for keying. Also, a protocol is defined for multiple data module readout and a broadcast method.

**Appendix A (VME64xP Type A-7U Subrack for 6U Modules)** This Appendix is an example of a purchase specification, consistent with Chapter 6, for a typical 7U subrack for housing 6U x 160 mm Modules and 6U x 80 mm Transition Modules.

**Appendix B (VME64xP Type A-10U Subrack for 9U Modules)** This Appendix is an example of a purchase specification, consistent with Chapter 6, for a typical 10U subrack for housing 9U x 400 mm Modules and 9U x 120 mm Transition Modules.

Appendix C (Keying for Subracks, Modules and Transition Modules) Keying and key codes are discussed in this Appendix. Sufficient flexibility is provided to accommodate users' needs for particular implementations while still preventing incompatible boards from being inserted into "incorrect" slots. This applies particularly, but not solely, with regard to power supply voltages

<u>Appendix D (Typical VMEbus Subrack Power Supplies)</u> This Appendix contains specifications for typical rack-mounted and rear-mounted power supplies, both switching and low-noise types, consistent with Chapter 7.

Appendix E (Chained Block Transfers (CBLT) and Multicast Commands (MCST)) This Appendix contains specifications for protocols to read out a group of modules using a daisy-chain and a single address cycle (CBLT). It also describes a broadcast mechanism (MCST) to set up and control CBLT and other operations for which a broadcast is useful.

## 1.5. VMEbus Overview

This section provides a short summation of the features of VMEbus based on a May 1996 VMEbus Journal article by John Rynearson of VITA. For details consult the specifications as indicated.

## 1.5.1. Address Space

The VME64 Specification, ANSI/VITA 1-1994, VME64, provides for 16 bit, 24 bit, 32 bit, 40 bit and 64 bit address spaces. These spaces are known as A16, A24, A32, A40 and A64 respectively. Six address modifier lines are used to distinguish address spaces and access modes.

A16, also known as short I/O address space, provides for 64 Kbytes of addressing and reduces address decoding for simple I/O boards.

The A24 address space requires only the P1/J1 VMEbus connector and provides a 16 Megabyte addressing space. Hence it is the standard address space used by 3U VMEbus Modules which have only a P1 connector. The P2 connector is used to provide the additional address and data lines needed to access 32 bits of address and data in non-multiplexed mode. Most contemporary 6U cards with both P1 and P2 connectors use A32 as their main addressing mode. The A32 space provides 4 GB of addressing space.

A40 allows for additional addressing space on 3U Modules by multiplexing the 24 bit address bus with the 16 bit data bus.

A64 allows for additional addressing space on 6U Modules by multiplexing the 32 bit data bus with the 32 address data bus to produce a 64 bit address cycle.

## 1.5.2. Data Transfer Cycles

The VME64 standard provides for 8 bit, 16 bit, 32 bit, and 64 bit data transfer cycles. Besides having different widths, data transfer cycles can be either single cycle or block transfer. Single cycle means that an address is sent with each data word while block transfer means that one address is followed by multiple data transfers. The VME64 specification brings multiplexed address and data cycles to both P1 only and to P1/P2 configurations.

Single cycle data transfer operations are labeled D8(O), D8(EO), D16, D32, and MD32. A D8 cycle can be either D8 (O) odd or D8 (EO) even and odd. From a hardware standpoint a 16 bit word is the basic unit on the VMEbus. Two data strobes, DS0\* and DS1\* are used to select the odd byte, the even byte, or both bytes within a 16 bit word. D8(0) provides for addressing odd bytes only using DS0\*. This reduces address decoding requirements for simple I/O boards while providing for accessing only the odd bytes in a defined memory space. On the other hand D8(EO) provides for access to both odd and even bytes. D16 accesses require only the P1 connector while D32 accesses require both the P1 and the P2 connectors. MD32 stands for multiplexed 32 bit transfers and is used primarily on 3U Modules to transfer 32 bits by multiplexing 16 bits of data on 16 of the possible 23 address lines. The MD32 mode allows a 2x speed enhancement using only the P1 connector. D64 is defined only for block transfers.

Block transfer operations improve data transfer efficiency by sending only one address for multiple bytes of data. These block transfer operations are labeled BLT, MBLT and A40BLT. BLT (BLock Transfer) operations provide for data transfer widths of 8 bits and 16 bits on P1 and 32 bits on P1/P2. MBLT (Multiplexed BLock Transfer) allows 64 bit transfers by multiplexing data onto the 31 address lines (A31-A1) and the LWORD\* control line. MBLT requires both the P1 and the P2 connector. A40BLT (A40 BLock Transfer) provides for 8, 16, and 32 bit multiplexed block transfers on a P1 only Module, primarily for 3U Module use.

Regarding interoperability between Modules with differing address and data capabilities, the VME64 Rules and Recommendations state:

- D16 Slaves MUST include D08(EO) capability.

- D16 Masters should include D08(EO) capability.

- D32 and MD32 Slaves MUST include D16 and D08(EO) capabilities.

- D32 and MD32 Masters should include D16 and D08(EO) capabilities.

- MBLT Masters should include D32, D16 and D08(EO) capabilities.

The VME64 specification provides data transfer capabilities from single cycle 8 bit transfers to multi-cycle 64 bit transfers and address spaces from 16 bits to 64 bits.

### 1.6. VME64 Extensions

VME64 Extensions, VITA 1.1-199x, greatly enhances VME64 for its use in many fields. The following new features are defined for optional usage in VME64x based applications.

- Addition of z & d rows to P1/J1 and P2/J2 connectors with associated pin assignments

- User defined 2 mm hard metric P0/J0 connector (area) between P1/J1 and P2/J2 with 95 user defined signal pins and a ground shield of either 19 or 38 pins

- 35 more signal grounds in P1/J1 and P2/J2

- +3.3 volt power pins

- Nominal 48 volt power pins primarily for DC-DC converters

- Three more +5 volt pins via the three VPC power pins

- Slot geographical address

- 12 reserved bus lines and 2 reserved unbused lines for future expansion

- 46 more user defined pins on P2/J2

- Test and Maintenance bus (T&M bus)

- Two mate-first-break-last precharge pins in P1/J1 and one pin in P2/J2 for live insertion

- Two mate-first-break-last ground pins in P1/J1 and one pin in P2/J2 for live insertion

- Two reserved pins for individual slot power control in live insertion applications

- Two bused serial lines for live insertion control

- EMC front panel

- ESD strips on boards and discharge clips on subrack card guides

- Solder side covers with ESD protection

- Injector/Extractor handles with optional locking feature

- User defined keying for boards and subrack slots

- Multifunction alignment pin

- Reserved area on front panel for ID and bar codes

- Rear I/O transition boards

- Added CR/CSR definitions

- Two-edged transfer protocols for higher throughput (2eVME)

- Expanded AM code capability with 2eVME

### 1.7. VME64xP Features

VME64xP Modules and Subracks are VME64x Modules and Subracks, respectively, in which many of the construction and protocol items given as options in VME64x are mandatory or recommended for enhanced interchangability and compatibility, increased I/O capability, and other characteristics and features desirable in physics applications and in other areas having similar requirements.

Various backplane configurations are selectable and the backplane requirements (all in strict compliance with VME64x) are specified in more detail. Pin assignments are made for the J0 connector for extra +5V power and power at other voltages while many pins are designated as grounds for enhanced signal quality. Also, pins are assigned as "user defined" in J0, that, together with those in the P2 connector, comprise an important feature of the VME64xP Subrack for applications requiring a large number of I/Os.

VME64xP Subracks are constructed to handle high power, for example for ECL circuitry. The high power necessitates adequate busing assemblies together with design and construction that permits sufficient and uniform cooling of the Modules, all of which are provided in VME64xP subracks. Also included are recommendations for EMC shielding of the Modules and subracks.

Injector/extractor handles, electrostatic discharge (ESD) provision, and keying (all optional in VME64x) are mandated in VME64xP Modules and Subracks. Also included are recommendations for EMC shielding of the Modules and Subracks.

VME64xP designates specific requirements for implementation of Configuration ROM (CR) and Control Space Register (CSR) space as well as for a Capabilities Register, and requires that data transfers to CR and CSR space be via D32. Addressing details are also specified or recommended both for operational efficiency and for uniformity.

The VME64xP standard includes also numerous recommended and suggested items and preferred implementations, many of which are readily available in VME64xP equipment (especially if specified as in Appendices for Type A and B VME64xP subracks).

Sections 1.7.1 and 1.7.2 list VME64xP items and their paragraph references that are not so specified in VME64x:

## 1.7.1. VME64xP Modules, Transition Modules, Power Transition Modules

- Specific protocol concerning address information latching (3.2-c), address modifier codes (3.2-e), response to BERR\* (3.3.3-c), and dynamic function size bit for Slave-terminated transfers (3.4-a, 3.4-b).

- Requires CSR Base Address Register (3.3.1-a) and Control Registers (3.3.2-b).

- Requires Geographical addressing (3.3.1-c).

- Requires and specifies additional Configuration ROM locations (3.3.2-b, 3.3.2-o) and Capabilities Register (3.3.2-b, 3.3.2-r).

- Requires P0 connector when implementing VME64xP defined signals or power (4.2-c)

- Requires that Transition Modules that use specified connectors have specified housings for alignment (4.4-i).

- Includes requirements for shields (4.2-j, -k) and electrostatic discharge features (4.2-s).

- Requires front panels (4.2-o), injector/extractor locking handles (4.2-t) and keying (4.2-v, 7.2-h) on Modules and Transition Modules.

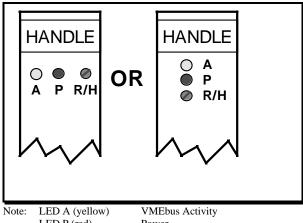

- Provides recommendations and suggestions regarding LED indicators for Activity, Power status, and Run/Halt (4.3-d,-e,-f,-g, 4.4-k, -l).

- Recommends maximum Module and Transition Module power dissipation (4.3-1, 4.4-m)

- Gives requirements for Power Transition Modules (Typically, a Power Transition Module would receive power through the backplane connector to power a DC-DC converter on the Transition Board and would route the converter generated power through backplane pins to a Module in the same slot.) (4.7.1-a, 4.7.1-c, 4.7.2-a, 4.7.2-c, and 4.7.2-d)

- Requires labels (4.2-x) and serial numbers (3.3.2-b) as described in VME64x.

- Specifies requirements for adapters for 3U and 6U Modules for use in subracks for 9U Modules (4.3-b).

## 1.7.2. VME64xP Subrack

- Specifies conformance to IEEE 1101.10 and 1101.11, to VME64x and VME64x 9U regarding 2 mm hard metric connectors, and to user specifications regarding loads (6.2-a).

- Requires provision for Transition Module card cage (6.4-a).

- Requires and specifies keying (6.2-f, 7.2-h) and slot numbering (6.2-e).

- Requires and specifies Module injector/extractor locking mechanism compatibility (6.2-h, 4.2-t).

- Provides requirements for EMC compatibility (6.2-i) top and bottom covers (6.2-j), and electrostatic discharge strips (6.2-k, 4.2-s).

- Specifies backplane flatness (6.3-d).

- Recommends backplane automatic electronic daisy chain jumpers (6.3.4-a).

- Requires protective shrouds for connectors with long pins extending from the rear of the backplane (6.3.1-d).

- Specifies pin assignments, busing and terminations for J0 connector (6.3.2-a).

- Specifies requirements for terminated TBus lines (6.3.3-a and 6.3.3-g).

- Specifies maximum differential voltage between backplane slots (6.3.5-a) and maximum voltage drop along a slot (6.3.5-b).

- Specifies sharing of common isolated return planes for some J0 voltages (6.3.5-e).

- Requires field-installable and removable GND connections to subrack frame (6.3.5-f).

- Specifies maximum backplane temperature rise (6.3.5-c).

- Specifies minimum current capacities (6.5-b) and maximum temperature rise of power supply connection assembly (6.5-e) and labeling of power connections (6.5-a).

- Recommends the insulation of bus bar outer surfaces (6.5-d).

- Provides specific restrictions to minimize obstruction to cooling air flow to Modules (6.7-a) and to Transition Modules (6.7-b).

- Requires that air flow through Module and Transition Module areas are independent of each other (6.7-c).

- Requires wiring and connections for remote sense (6.6-a) and specifies maximum voltage drop from subrack power supply connection to backplane connector pins (6.5-f).

- Mandates bus voltage specifications (7.2-a).

## 1.8. Software

Software is as important as hardware in VMEbus systems. This document does not deal with software but several VMEbus related software documents do exist and are listed below. Copies of these standards can be obtained from the VITA office.

- VITA 19-1997 draft standard provides a common method for use by two or more devices (participants

or peers) for network communication across a backplane. The protocol is context independent so most

high level networking protocols can be used by peers on the same backplane.

- VITA 25-199x draft standard addresses software issues which may be of interest to users of this

document. This standard is an Application Program Interface for VMEbus called VISION (Versatile

I/O Software Interface for Open-bus Networks).

This page intentionally left blank

## 2. Interpretations, Definitions, Acronyms & References

## 2.1. Interpretation of this Document

To avoid confusion, and to make clear the requirements for compliance, many of the paragraphs in this document are labeled with keywords that indicate the type of information they contain. The keywords are listed below:

#### Rule:

Rules form the basic framework of the VMEbus specification. They are sometimes expressed in text form and sometimes in the form of figures or tables. Rules indicate items that are mandatory for compliance with this document. The words *shall* and *shall not* are reserved exclusively for stating rules in this document.

#### **Recommendation:**

Wherever a recommendation appears, designers would be wise to take the advice given. Doing otherwise might result in poor performance or other problems. While the VMEbus, VME64, VME64 Extensions and VME64xP architectures support high performance systems, it is possible to design a system that complies with all the rules, but has insufficient performance. In many cases, a designer needs a certain level of experience with VMEbus in order to design boards that deliver top performance. Recommendations found in this standard are based on this kind of experience and are provided to help designers. The words *should* and *should not* are reserved exclusively for stating recommendations.

#### **Permission:**

In some cases a rule does not specifically prohibit a certain design approach, but the reader might be left wondering whether that approach might violate the spirit of the rule or whether it might lead to some subtle problem. Permissions reassure the reader that a certain approach is acceptable. The word *may* is used for stating permissions in this document but is also used in a more general sense.

#### **Suggestion:**

A suggestion contains advice which is helpful but not vital. The reader is encouraged to consider the advice before discarding it. Some decisions that need to be made are difficult until experience has been gained.

#### **Observation:**

Observations do not offer specific advice. They provide information and sometimes follow naturally from what has been discussed. They spell out the implications of certain rules and bring attention to things that might otherwise be overlooked. They also give the rationale behind certain rules so that the reader understands why the rule is to be followed.

## 2.2. Notations and Logic Signal Conventions

Signal names refer to both single signals and logical signal groups. Groups of signals are indicated by the name of the signal followed by the range of signals within the group in parentheses as shown here:

XX(M:N) where: XX => bus signal name

$(M:N) \ \ => \ range \ of \ signal \ name$

M => maximum number

N => minimum number

example: DATA(31:0) represents DATA31, ••• DATA1, DATA0

The notation for AM (or XAM) codes are as follows:

NN => AM code, decimal

0xNN => AM code, hexadecimal

Addresses or data are specified in hexadecimal with various lengths as appropriate. The notations are as follows:

$0xN \cdot \cdot N =$ Hexadecimal value where each "N" is a nibble

where  $N = 0, 1, \bullet \bullet E$ , F. The format,  $0xN \bullet \bullet N$ , is consistent with C programming notation.

Signals are named for active high TTL signals. Where the active state of the signal is low the signal name has a "\*" appended to the name. For example the address synch, AS, signal is active low so the signal is referred to as AS\*.

#### 2.3. Definitions

## 2.3.1. VME64xP Definitions

Terms used in this document are defined in (1) the VMEbus Specification, Section 1.2.1 (Basic Definitions), or (2) the VME64 Specification, Section 1.2.2 (Basic Definitions), or (3) this section.

- <u>VME64xP Module:</u> A VMEbus Circuit Board, front panel and any other parts which make up a plugin unit that is inserted in the front of the subrack, mates with the front of the backplane and conforms to the requirements of Chapter 4 and all other pertinent Rules in this document.

- <u>VME64xP Transition Module:</u> A VMEbus Transition Board, front panel and any other parts which make up a plug-in unit that is inserted in the rear of the subrack, mates with the rear of the backplane and conforms to the requirements of Chapter 4 and all other pertinent Rules in this document.

- <u>VME64xP Subrack</u>: A VMEbus subrack which also conforms to the requirements of Chapter 6 and all other pertinent Rules in this document. VME64xP Modules and other VMEbus Modules are inserted in the front of the subrack while Transition Modules are inserted in the rear of those subracks that have rear mounted card cages for Transition Modules. (Subrack corresponds to "Crate" in CAMAC and "Bin" in NIM.)

- <u>Board, Circuit Board, Transition Board:</u> Other VMEbus documents use the term <u>Board</u> to refer to the entire Module. In this document <u>Board</u> is used as a generic term while the board that mates with the front of the backplane (and may or may not be within a Module) is designated the <u>Circuit Board</u>. The board that mates with the rear of the backplane is designated the <u>Transition Module</u>.

- <u>A(31:0):</u> This document uses the VME64x terminology for addresses, *e.g.* A(31:0). The notation, A(31:1), LWORD\* which is used in VME64 is not used here. LWORD\* in VME64x and in this document is treated as A(0).

#### 2.3.2. Other Definitions

Specific terms found in this document that may not be familiar to all readers include:

- <u>Ground (GND):</u> A wire, conductor or plane which provides the path for current to return to the power supply from the circuit. A GND is not Earth as sufficient current through GND can cause it to develop voltage differences from other returns in the power supply system. Typically return current from digital circuitry flows through GND. Ideally GND is connected to Earth in only one place in a system.

- Earth Ground (Earth): A point which is used as a base reference for multiple subsystems and, if used, is typically provided through a long conductive rod driven into the soil to provide sub-milliohm resistance. A point of minimum potential in the circuit which does not appreciably vary with changes in current through the point. See also VME64x, Section 8.2.5 for resistances in Earth and GND as related to safety.

- <u>Reference Voltage:</u> This is a voltage used in analog circuitry as a reference to which other signals are compared. The reference circuit ideally has no current flow. Since no current flows, this point is very stable under all conditions and the same voltage at all points.

- <u>Shield:</u> The conductive case which surrounds electronics and serves to inhibit the radiation or reception of EMI. It is typically connected to Earth.

- <u>Reserved</u>: Connector contacts, register bits, etc. that are reserved are not to be used until assigned by VIPA or VSO.

- <u>Set-Reset Register Pair:</u> A combination of Control/Status Registers (CSR) in which writing a one to a bit in one register sets a function and writing a one to the same bit in the other register resets that function. Set-Reset registers simplify software in that changes to some of the bits can be accomplished without affecting the other bits, removing the necessity of read-modify-write cycles at the cost of requiring two bits per control function.

## 2.3.3. Acronyms

BAR: Base Address Register

BLLI: Board Level Live Insertion

CR: Configuration ROM

CSR: Control and Status Register

EMC: Electromagnetic Compatibility

EMI: Electromagnetic Interference

• ESD: Electrostatic Discharge

<u>LVDS:</u> Low Voltage Differential Signals

MBLT: Multiplexed BLock Transfer

• PSAB: Power Supply Attachment Bulkhead

• TBUS Timing Bus (tri-state)

• <u>TBUSOC</u> Timing Bus (open collector)

<u>VIPA:</u> VMEbus International Physics Association

<u>VITA:</u> VMEbus International Trade Association

• <u>VME:</u> IEEE 1014-1987 (IEC 821)

• VME64: ANSI/VITA 1-1994

• <u>VME64xP:</u> The designation of this document and of items (equipment, protocols, etc.)

conforming to this document

VME64x: VME64 Extensions - VITA 1.1-199x Draft Standard

• VPC: Voltage Precharge

• <u>VSO:</u> VITA Standards Organization

• <u>2eVME</u>: 2 edge VMEbus operations for block transfers

• VME64x9U: VME64x 9U x 400mm Format - VITA 1.3-199x Draft Standard

## 2.4. Other References

A VITA 23 Designer & User Guide (DUG) which contains supplementary information to this document is being developed. The Users Guide is not a standard but rather is structured to have useful information for designers of VMEbus and VME64xP equipment. The DUG will be updated as information which could be useful becomes available. Users of this document are encouraged to periodically check for the latest version which can be downloaded from the VITA server listed below.

The VMEbus International Trade Association (VITA) World Wide Web home page contains a pointer to VMEbus products and a wealth of other useful information. The VITA World Wide Web page can be accessed at the following URL (Universal Resource Locator):

## http://www.vita.com

## 3. Address Modes, Data Widths, and CR/CSR Definitions

### 3.1 Introduction

VME64xP Modules comply with the mandatory requirements of VME64 and VME64x specifications. This chapter describes and specifies the additional requirements for VME64xP Modules which enhance compatibility and functionality for research.

#### Observation 3.1-a (LWORD\* usage):

This document uses the VME64x terminology for addresses, *e.g.* A(31:0). The notation, A(31:1), LWORD\* which is used in VME64 is not used here. LWORD\* in VME 64x and here is now treated as A(0).

## 3.2 Additional Addressing & Data Width Requirements

## Recommendation 3.2-a (A32 & A64 capability):

A VME64xP Module with a data space of less than or equal to 128 MB (27 bits) should have its data space accessed by A32 addressing. A larger data space within the Module should be accessed by A64 addressing.

## Observation 3.2-b (A32, A64 addressing & D32, D64 data widths):

The emphasis in current and future VME specifications is towards Module implementations supporting combinations of A32 and A64 addressing and D32 and D64 data widths.

## Recommendation 3.2-c (address information latching):

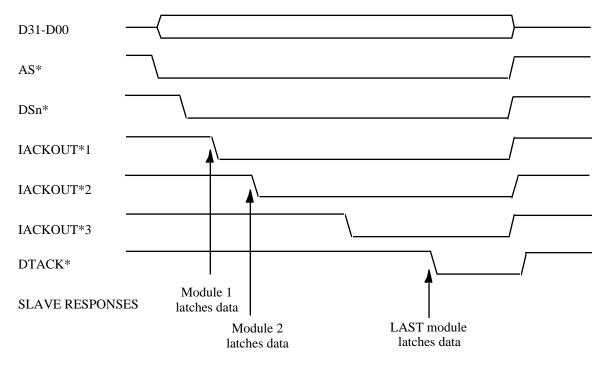

For all non-A64 VMEbus operation address cycles, VME64xP Slaves should at a minimum latch the signals on the AM(5:0) and A(31:0) signal lines during the address cycle at the falling edge of the AS\* signal. For all A64 VMEbus operation address cycles, VME64xP Slaves should additionally latch the signals on the D(31:0) signal lines during the address cycle at the falling edge of the AS\* signal.

## Observation 3.2-d (latching address and pipelining):

Since address pipelining is permitted in VME, Slaves may need to delay the latching of the address and address modifier lines until they complete the current operation.

#### **Recommendation 3.2-e (preferred AM codes):**

The AM codes in Table 3.2-1 are preferred and should be used to access VME64xP Modules.

## Rule 3.2-f (data path width):

VME64xP Modules shall support D32 transfers.

## Observation 3.2-g (data packing into D32 transfers):

Higher throughput during block transfers is achieved if a Module packs words and/or bytes into 32 bit transfers during read data cycles and accepts 32 bit transfers during write data cycles.

## Recommendation 3.2-h (support of D64):

VME64xP Modules should support D64 block transfers.

Table 3.2-1 Addressing Classifications in VMEbus, VME64 and VME64x VME64xP Preferred AM Codes

| Addressing<br>Classification | Applicable<br>Standard | Defined AM Codes<br>(hexadecimal) | Function<br>all non privileged                         |

|------------------------------|------------------------|-----------------------------------|--------------------------------------------------------|

| A24                          | VME64                  | 2F                                | D32 CR/CSR Space                                       |

| A32                          | VMEbus                 | 08<br>09<br>0B                    | D64 MBLT<br>D32 single transfer<br>D32 BLT             |

| A32                          | VME64x                 | 20                                | D64, 2eVME for 6U                                      |

| A64                          | VME64                  | 00<br>01<br>03                    | D64 MBLT<br>D32 single transfer<br>D32 (preferred) BLT |

| A64                          | VME64x                 | 20                                | D64, 2eVME for 6U                                      |

#### Observation 3.2-i (support of MBLT and 2eVME, etc.):

Data transfer rates may be improved if VME64xP modules implement 64 bit data transfers and high speed data transfer protocols such as MBLT and 2eVME.

## Observation 3.2-j (data packing and 64-bit transfers):

Data throughput is increased when data is efficiently 'packed'. For example, if the valid data word length internal to the Module to be read is 32-bits, data throughput is doubled if the Module 'packs' two valid 32-bit words into every 64-bit VMEbus read cycle according to the byte order defined in VME64.

## 3.3 Accessing CR/CSR Registers & Additional CR/CSR Requirements

The assignment and usage of Configuration ROM/Control and Status Registers (CR/CSR) for VME64xP Modules follows the methods suggested in VME64 and VME64x. In this document some of the features in these two documents are made mandatory. The standardization of certain registers will aid software in managing data acquisition systems.

## 3.3.1 Base Address Register

The following Rules are based on VME64 Chapter 2 and VME64x Chapter 3 for access to CR/CSR space. This section makes certain optional implementations in those documents mandatory. These VME64xP CR/CSR requirements are supported by IC interfaces for the implementation of the VME64x standard and should pose little or no extra overhead on the design of modules.

#### Rule 3.3.1-a (Base Address Register implementation):

VME64P Modules shall implement a Base Address Register (BAR) in accordance with VME64 (Chapter 2, Section 2.3.12), VME64x (Chapter 3, Section 3.2.11 and the Rules in this section.

#### Observation 3.3.1-b (BAR location):

The Base Address Register is at address offset 0x7FFFF.

### Rule 3.3.1-c (default loading of the CR/CSR Base Address Register):

VME64xP Slave Modules shall load their CR/CSR Base Address Register with the Module's Geographical Address upon power-on or upon any board reset condition,

including the receipt of the SYSRESET\* signal. The Geographical Address shall be loaded into BAR bits (7:3).

### **Observation 3.3.1-d (polarity of GA pin levels):**

GA pins are low-true signals on a VME backplane.

## **Observation 3.3.1-e (changing the BAR):**

The contents may be changed by writing a new value into the BAR.

## Rule 3.3.1-f (using the Base Address Register to access CR & CSR registers):

A Modules Configuration ROM (CR) and Control/Status Register (CSR) registers shall be accessed by AM code 0x2F with A24 addressing.

## Observation 3.3.1-g (CR/CSR addressing details):

During a CR/CSR access, bits (7:3) of the BAR are compared to the state of address lines A(23:19) respectively. If a match is found, address bits A(18:0) are used to access the Modules CR or CSR registers.

## 3.3.2 Control Registers

The standardization of CR registers is important to system software for the configuration and monitoring of subracks containing VMEbus modules. The CRs have information which can be used by a Monarch or other Master to determine a Modules features, history, operation manual, *etc*. The VME64 and VME64x implementation of the CR registers is structured so a byte wide PROM, ROM or other similar device can easily be used to store the information. The same interface ICs utilized for the Base Address Register (3.3.1) have features to make CR register implementation simple for the board designer. The CRs in this section are based on the registers discussed in VME64, Section 2.3.12 and VME64x, Chapter 10.

This Section additionally specifies one VME64xP CR and reserves an additional fifteen bytes for possible future standardization. The user is free to use the remaining User CR space as desired.

#### Rule 3.3.2-a (implementation of CR registers):

CR registers that are implemented in VME64xP shall be in accordance with VME64x (Chapter 10), and the Rules in this Chapter.

Table 3.3.2-1 VME64xP Module Configuration ROM (CR) Registers

| Address Offset         | CR Register Content                  | Size   | Standard |

|------------------------|--------------------------------------|--------|----------|

| 0x03                   | Checksum                             | 1 byte | VME64    |

| 0x07, 0x0B, 0x0F       | Length of ROM                        | 3 byte | VME64    |

| 0x13                   | Configuration ROM data access width  | 1 byte | VME64    |

| 0x17                   | CSR data access width                | 1 byte | VME64    |

| 0x1B                   | CR/CSR Space Specification ID        | 1 byte | VME64    |

| 0x1F                   | 0x43 (ASCII "C")                     | 1 byte | VME64    |

| 0x23                   | 0x52 (ASCII "R")                     | 1 byte | VME64    |

| 0x27, 0x2B, 0x2F       | Manufacturer's ID (IEEE OUI)         | 3 byte | VME64    |

| 0x33, 0x37, 0x3B, 0x3F | Board ID supplied by manufacturer    | 4 byte | VME64    |

| 0x43, 0x47, 0x4B, 0x4F | Revision ID supplies by manufacturer | 4 byte | VME64    |

| 0x83, 0x87, 0x8B       | Offset of BEG_SN (serial number)     | 3 byte | VME64x   |

| 0x8F, 0x93, 0x97       | Offset of END_SN (serial number)     | 3 byte | VME64x   |

| 0xB3, 0xB7, 0xBB       | BEGIN_USER_CR                        | 3 byte | VME64x   |

| 0xBF, 0xC3, 0xC7       | END_USER_CR                          | 3 byte | VME64x   |

| C(BEGIN_USER_CR)       | VME64xP Capabilities                 | 1 byte | VME64xP  |

## Rule 3.3.2-b (mandatory VME64xP CR registers):

VME64xP Modules shall implement all CR registers listed in Table 3.3.2-1.

### **Observation 3.3.2-c (compatibility with VME64x):**

With the exception of the VME64xP Capabilities register, the CRs specified in Table 3.3.2-1 and Table 3.3.2-2 are a subset of the CRs in VME64x, Table 10-12.

#### Rule 3.3.2-d (Slave characteristic register):

VME64xP Slaves shall implement the Slave Characteristic register in Table 3.3.2-2.

#### Rule 3.3.2-e (Master characteristic register):

VME64xP Slaves shall implement the Master Characteristic register in Table 3.3.2-2.

## **Rule 3.3.2-f (Interrupt handler register):**

VME64xP Interrupt Handler Modules shall implement the Interrupt handler register in Table 3.3.2-2.

## Rule 3.3.2-g (Interrupt capabilities register):

VME64xP Modules with interrupts shall implement the Interrupt capabilities register in Table 3.3.2-2.

Table 3.3.2-2 Characteristics and Capabilities Registers

| Address Offset | CR Register Content              | Size   | Standard            |

|----------------|----------------------------------|--------|---------------------|

| 0xE3           | Slave Characteristics Parameter  | 1 byte | VME64x <sup>1</sup> |

| 0xEB           | Master Characteristics Parameter | 1 byte | VME64x <sup>1</sup> |

| 0xF3           | Interrupt handler Capabilities   | 1 byte | VME64x <sup>1</sup> |

| 0xF7           | Interrupter Capabilities         | 1 byte | VME64x <sup>1</sup> |

Note 1: Details are in VME64x, Section 10.2.1.3.

#### Rule 3.3.2-h (Slave Characteristic Registers):

VME64xP Modules that utilize Address Space Relocation features described in VME64x, Chapter 10 shall implement the necessary Configuration ROM registers listed in VME64x Table 10 12. These registers are from address offset 0x103 through 0x74F.

## Rule 3.3.2-i (other CR registers):

If CR registers other than those in Table 3.3.2-1 are implemented in a Module, they shall be implemented in accordance with VME64x, Chapter 10 and this chapter.

## Recommendation 3.3.2-j (VME64xP Module Configuration ROM implementation):

The Configuration ROM should be implemented with eight-bit, non-volatile memories or other re-programmable device.

## Observation 3.3.2-k (address of CR bytes):

The data in the Configuration ROM is at every fourth byte address.

## Observation 3.3.2-1 (reading a single-byte Configuration ROM in D32 mode):

When reading a single-byte from the Configuration ROM in D32 mode, the relevant data will be read from the lowest order byte, with the upper three bytes undefined.

#### Observation 3.3.2-m (byte order):

Multi-byte information is stored in big-endian order, *i.e.* the most significant byte is at the lowest address.

### Observation 3.3.2-n (Reserved and unused User bits):

VME64x requires all Reserved and unimplemented User bits to be read as logical zero.

## Rule 3.3.2-o (VME64xP Module Configuration ROM):

If a VME64xP Module implements additional VME64xP CR registers, they shall be implemented as in Table 3.3.2-3.

Table 3.3.2-3 VME64xP Module Configuration ROM

| CR Address Offset<br>[MSBLSB] | Contents                | Size                  |

|-------------------------------|-------------------------|-----------------------|

| $C(BEG\_USER\_CR) = Y$        | VME64xP Capabilities CR | 1 byte                |

| $(Y + 0x4) \dots (Y + 0x3C)$  | Reserved, set to 0      | 15 bytes <sup>1</sup> |

| (Y+ 0x40) C(END_USER_CR)      | User Defined            |                       |

Note 1: See Recommendation 3.3.2-j, Observation 3.3.2-k, -l and -m for byte location in the specified address range.

## **Observation 3.3.2-p (Configuration ROM starting address):**

The part of the Configuration ROM space specified in Table 3.3.2-3 starts at the offset address in BEG\_USER\_CR as defined in VME64x, Chapter 10.

## **Observation 3.3.2-q (User Configuration ROM pointers):**

In Table 3.3.2-3, Y denotes the contents of the BEG\_USER\_CR. A pointer to the end of User CR space (END\_USER\_CR) as defined in VME64x is also needed.

## Rule 3.3.2-r (VME64xP Capabilities Register bits):

The bits in the VME64xP Capabilities Register shall be as specified in Table 3.3.2-4.

Table 3.3.2-4

VME64xP Capabilities Register Bit Assignments

| VME64xP<br>Capabilities<br>Register Bit | Meaning if Set<br>(bit reads back as logic 1) | Meaning If Clear<br>(bit reads back as logic 0) |

|-----------------------------------------|-----------------------------------------------|-------------------------------------------------|

| 0                                       | Module has Byte Count Register                | No Byte Count Register                          |

| 1                                       | Module has Self Test Register                 | No Self Test Register                           |

| 2                                       | User Defined <sup>1</sup>                     | User Defined <sup>1</sup>                       |

| 3                                       | User Defined <sup>1</sup>                     | User Defined <sup>1</sup>                       |

| 4                                       | Reserved <sup>1</sup>                         | Reserved <sup>1</sup>                           |

| 5                                       | Reserved <sup>1</sup>                         | Reserved <sup>1</sup>                           |

| 6                                       | Reserved <sup>1</sup>                         | Reserved <sup>1</sup>                           |

| 7                                       | Reserved <sup>1</sup>                         | Reserved <sup>1</sup>                           |

Note 1: See Observation 3.3.2-n.

### **Observation 3.3.2-s (byte count register):**

The bit which denotes the byte count register capability is potentially redundant since this information can be determined by the setting of the DFS bit in the data space's ADEM. See Rule 3.4-a.

## 3.3.3 VME64xP Control/Status Registers

The VME64xP CSR specification follows the recommendations in VME64x, Chapter 10 for User CSRs. This Section specifies reserves sixteen bytes for possible future standardization. The user is free to define the remaining User CSR space as desired.

## Rule 3.3.3-a (implementation of CSR registers):

The implementation of VME64xP CSRs in User Space shall be as in Table 3.3.3-1.

## **Observation 3.3.3-b (VME64xP CSR pointers):**

The CSRs in Table 3.3.3-1 start at the offset address in BEG\_USER\_CSR as defined in VME64x, Chapter 10. In Table 3.3.3-1, X denotes the contents of the BEG\_USER\_CSR register which is a pointer to the start of User CSR space defined in VME64x. A pointer to the end of User CSR space (END\_USER\_CSR) as defined in VME64x is also needed.

Table 3.3.3-1 VME64xP Module Control/Status Register (CSR)

| CSR Address Offset<br>[MSBLSB] | Content          | Size                  |

|--------------------------------|------------------|-----------------------|

| C(BEG_USER_CSR) (X+0x3C)       | VME64xP Reserved | 16 bytes <sup>1</sup> |

| (X+0x40) C(END_USER_CSR)       | User Defined     |                       |

Note 1: See Recommendation 3.3.2-j, Observation 3.3.2-k, -l and -m for byte location in the specified address range.

## Rule 3.3.3-c (BERR\* issued flag):

A VME64xP Module which issues BERR\* shall implement Bit 3 of the CSR Bit Set and Bit Clear Registers as defined in VME64x, Chapter 10.

## Rule 3.3.3-d (Address Space Relocation Registers):

VME64xP Modules that utilize the Address Space Relocation feature(s) described in VME64x, Chapter 10 shall implement the CSR ADER register(s) listed in VME64x Table 10 13. These registers are from address offset 0x7FFD3 through 0x7FF6F.

## 3.4 Variable-Length Readout

Some data acquisition modules prepare an arbitrary amount of data for readout. A Master may not have prior knowledge of the amount of data in such a module. Prior to the 2eVME protocol (VME64x, Chapter 11), the only mechanism for variable-length readout was for the master to request the maximum possible amount of data, and the slave to drive BERR\* when no more data is available. Many existing VMEbus master interfaces map BERR\* to the CPU's bus error mechanism. Memory-protected operating systems such as UNIX and Windows NT treat a bus error in kernel mode as a fatal condition, which results in a kernel panic and reboots the system. Since VME64xP slaves will probably be used with older master interfaces and the aforementioned software, it is desirable to specify a generic variable-length readout mechanism.

VME64x Chapter 10, defines a mechanism for supporting Address Space Relocation (programmable address decoding) for up to eight "functions" within a slave. Using this scheme, a master designated as the "system monarch" can discover all slave functions in the system and program their address ranges. One of its "advanced" features is "dynamic function sizing", which means that it supports the possibility that a function's size may not be hardwired. This can be used to allow effective slave-terminated transfers using masters which do not support 2eVME. To do this, one uses the function's "ADER" (Address DEcoder compaRe register) to allow the master to read, immediately before the transfer, the amount of data which is

available. The VME64x mechanism has some hardware complexities associated with it. As large scale interface chips become available these issues will disappear. The readout technique described in Appendix E may be a viable alternative for designers.

## Rule 3.4-a (DFS bit):

If a VME64xP Slave implements Slave-terminated transfers, then the DFS (Dynamic Function Size - bit 2) bit shall be set in the ADEM (Address DEcoder Mask).

### Rule 3.4-b (ADER Register):

A VME64xP Slave obeying Rule 3.4-a shall use bits (31:8) of the corresponding function's ADER (Address DEcoder compaRe register) for containing the byte count whenever its DFSR (Dynamic Function Size Read - bit 1) bit is set.

## **Observation 3.4-c (transfer count):**

Rule 3.4-b allows a maximum of  $2^{24}$ -1 bytes for such transfers. The byte count may be for the current transfer, total transfer, or any other transfer as defined by the user. The user should note that the maximum byte count is 2K for D64 block transfers as defined in VME64 and VME64x.

#### **Observation 3.4-d (ADER conflicts):**

Since the primary purpose of the ADER's C(31:8) bits is to allow software to set the base address at which a function resides, defining this alternate read behavior can introduce a conflict if care is not taken.

## **Recommendation 3.4-e (maintaining base address):**

VME64xP Slaves obeying Rule 3.4-b should maintain separate logic paths for reading and writing the ADER's C(31:8) bits. That is, they should continue responding at the last programmed base address while latching byte counts for reading. This avoids the potential conflict mentioned in Observation 3.4-d.

9-Dec-97

This page intentionally left blank

## 4. VME64xP Modules and Transition Modules

### 4.1 Introduction

This chapter contains details concerning the construction of VME64xP Modules and Transition Modules. Sections 4.2, 4.5, 4.6 are common to both, while Section 4.3 is specific to the VME64xP Module, Section 4.4 to the VME64xP Transition Module and Section 4.7 is specific to the VME64xP Power Transition Module.

VME64xP Modules are fully compliant with VME64 and VME64x, but VME64 and VME64x modules are not necessarily compliant to the VITA 23 (VME64xP) specifications in this document. VME64xP Transition Modules are fully compliant with VME64x.

## **4.2 General Specifications**

### Recommendation 4.2-a (9U board thickness):

The thickness of 9U VME64xP Module and Transition Module Circuit Boards should be  $2.4 \pm 0.2 \text{ mm}$  (0.093  $\pm 0.008 \text{ inch}$ ).

## **Observation 4.2-b (edge thickness):**

Circuit Boards which are thicker than 1.6 mm will have to be milled in the card guide area on the solder side, as specified in IEEE 1101.1.

#### Rule 4.2-c (P0 connector):

VME64xP Modules shall implement the P0 connector specified in VME64x, Chapter 4, when implementing VME64xP defined signals or power listed for J0 in Table 6.3.2-1.

#### **Recommendation 4.2-d (P4 connector):**

If a VME64xP Module has a P4 connector, it should be the 95 signal contact, IEC 61076-4-101, Style B, 2 mm hard metric with top shield.

### **Recommendation 4.2-e (P5 connector):**

If a VME64xP Module has a P5 connector, it should be the 110 signal contact, IEC 61076-4-101, Style B, 2 mm hard metric with top shield.

## Recommendation 4.2-f (P6 connector):

If a VME64xP Module has a P6 connector, it should be the 110 signal contact, IEC 61076-4-101, Style A, 2 mm hard metric with top shield.

#### Permission 4.2-g (alternate P6):

A 125 signal contact IEC 61076-4-101, Style B, 2 mm hard metric with top shield may be used for P6.

#### **Observation 4.2-h (alternate P6 size and pins):**

The connector in Permission 4.2-g is the same overall size as the connector specified in Recommendation 4.2-f. Style A connectors have fifteen contacts in the center replaced by a guide/key mechanism.

#### Permission 4.2-i (P3 connector):

A P3 connector conforming to IEC 60603-2 or IEC 61076-4-1xx may be used on VME64xP Modules in place of P5 and P6.

modstm.doc 4-1

#### **Rule 4.2-j (P0 shield):**

A VME64xP Module shall use an upper (component side) shield for the P0 connector described in VME64x, Chapter 4.

#### Recommendation 4.2-k (P0, P4, P5, P6 bottom shield):

The lower (solder side) shield should be used for the IEC 61076-4-101 connectors described herein.

## Observation 4.2-1 (P0, P4, P5, P6 extra grounds):

The lower (solder side) shield provides extra ground paths to reduce inductive noise and also provides additional EMI shielding.

#### Rule 4.2-m (connection of shields):

All shield(s) shall be connected to GND (digital return).

## **Observation 4.2-n (connector mating):**

The use of connectors other than those specified in Recommendation 4.2-d, e, f or Permission 4.2-i may cause difficulties in construction. The specified connectors have datums which are the same as the P1 and P2 connectors and thereby ensure proper mating.

### Rule 4.2-o (general front panel rules):

VME64xP 6U and 9U Modules shall have front panels in accordance with IEEE 1101.10. VME64xP Transition Modules shall have front panels in accordance with (IEEE) P1101.11.

## Rule 4.2-p (EMC front panels):

Front panels for Modules and Transition Modules shall have provisions for EMC front-panel gaskets as in IEEE 1101.10 and (IEEE) P1101.11.

## **Recommendation 4.2-q (solder side covers):**

Solder side covers as described in IEEE 1101.10 should be used on Modules and Transition Modules to prevent the solder side of Module and Transition Module Circuit Boards from shorting or abrading the EMC gaskets on adjacent modules.

#### **Observation 4.2-r (cover thickness and component height):**

The space available for components on the solder side is minimal. The distance from the component side of the printed circuit board to the outside of the solder side cover is 4.0 mm maximum. This dimension includes the board thickness, solder side component height and the cover thickness.

## Rule 4.2-s (ESD strips):

ESD strips discussed in VME64x, Chapter 8, shall be used on all VME64xP Module and Transition Module Circuit Boards.

#### **Rule 4.2-t (injector/extractor/locking handles):**

The Injector/Extractor handles specified in IEEE 1101.10 shall be used on all VME64xP Modules and Transition Modules. A self locking feature shall be implemented on these handles which is compatible with the IEEE 1101.10 and IEEE 1101.11 mechanics.

#### **Observation 4.2-u (locking handle and screws):**

The need for front panel retention screws is removed since the locking handles are less susceptible to vibration problems.

#### Rule 4.2-v (keving):

VME64xP Modules and Transition Modules shall have keying as in VME64x, Chapter 7.

modstm.doc 4-2

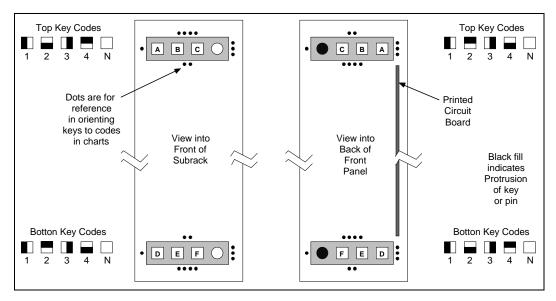

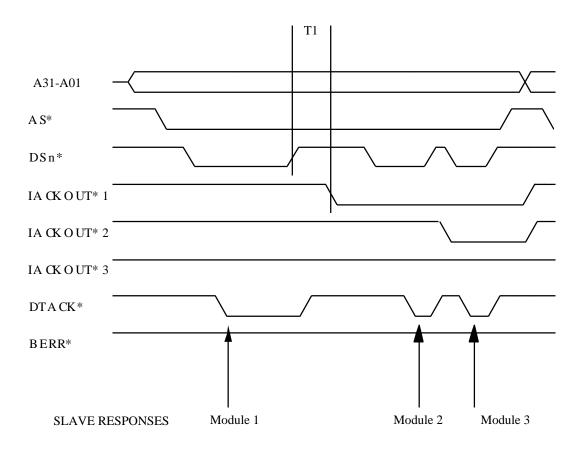

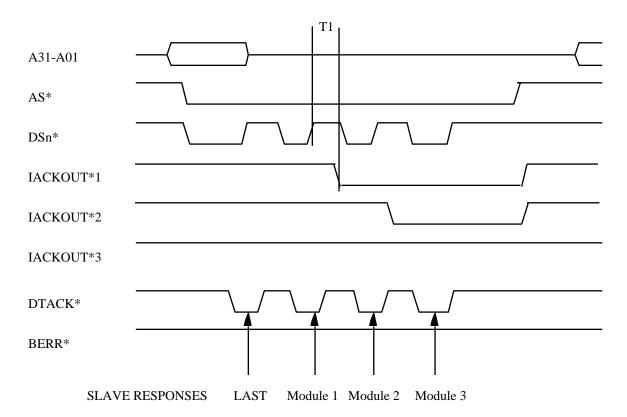

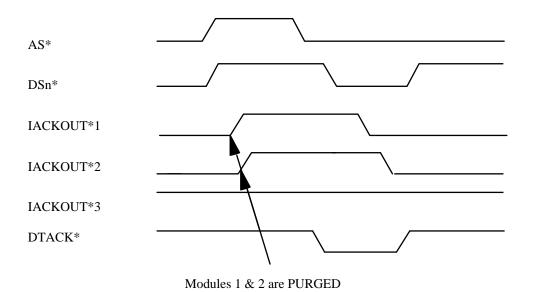

#### **Recommendation 4.2-w (Module keying guidelines):**