## **XZ030**

# USER MANUAL FAMILY OF ANALYZERS

Models covered:

AP235/AP240 with SSR

AP235/AP240 with AdvancedTDC

AP101/AP201

January 2006

The information in this document is subject to change without notice and may not be construed in any way as a commitment by Acqiris. While Acqiris makes every effort to ensure the accuracy and contents of the document it assumes no responsibility for any errors that may appear.

All software described in the document is furnished under license. The software may only be used and copied in accordance with the terms of license. Instrumentation firmware is thoroughly tested and thought to be functional but it is supplied "as is" with no warranty for specified performance. No responsibility is assumed for the use or the reliability of software, firmware or any equipment that is not supplied by Acqiris SA or its affiliated companies.

Any versions of this manual which are supplied with a purchased product will be replaced at your request with the latest revision in electronic format. At Acqiris we appreciate and encourage customer input. If you have a suggestion related to the content of this manual or the presentation of information, please contact your local Acqiris representative or Acqiris Technical Support (support@acqiris.com) or come visit our web site at <a href="http://www.acqiris.com">http://www.acqiris.com</a>.

Trademarks: product and company names listed are trademarks or trade names of their respective companies

Acqiris Headquarters : Acqiris USA : Acqiris Asia-Pacific :

**Acgiris SA Acgiris LLC Acgiris Pty Ltd** 18, chemin des Aulx 234 Cromwell Hill Rd. Suite 7, Level 1. 407 Canterbury Road, CH-1228 Plan-les-Ouates P.O. Box 2203 Geneva Monroe, NY 10950-1430 P.O. Box 13 **Switzerland** USA **Surrey Hills 3127** Australia

Tel: +41 22 884 33 90 Tel: 845 782 6544 Tel: +61 3 9888 4586 Fax: +41 22 884 33 99 Fax: 845 782 4745 Fax: +61 3 9849 0861

© Copyright January 2006, Acqiris SA. All rights reserved.

# **CONTENTS**

| 1. | OUT           | OF THE BOX                                                   | 6  |

|----|---------------|--------------------------------------------------------------|----|

|    | 1.1.          | Message to the User                                          | 6  |

|    | 1.2.          | Using this Manual                                            | 6  |

|    | 1.3.          | Conventions Used in This Manual                              |    |

|    | 1.4.          | Disclaimer and Safety                                        |    |

|    | 1.5.          | Warning Regarding Medical Use                                |    |

|    | 1.6.          | Packaging and Handling                                       |    |

|    | 1.7.          | Warranty                                                     |    |

|    | 1.8.          | Warranty and Repair Return Procedure, Assistance and Support |    |

|    | 1.9.          | System Requirements                                          |    |

|    | 1.10.         | Transport & Shipping                                         |    |

|    |               | · · · · · · · ·                                              |    |

|    | 1.11.         | Maintenance                                                  |    |

|    |               | Cleaning                                                     |    |

|    | 1.13.         | Disposal and Recycling                                       | 9  |

| 2. | INS           | FALLATION                                                    | 10 |

|    | 2.1.          | Installing the Software under Windows                        | 10 |

|    | 2.1.<br>2.1.1 |                                                              |    |

|    | 2.1.1         | č                                                            |    |

|    | 2.1.2         | 1                                                            |    |

|    |               | Installing the Software for Linux                            |    |

|    | 2.2.<br>2.2.1 | -                                                            |    |

|    | 2.2.1         | <u>.</u>                                                     |    |

|    | 2.2.3         | •                                                            |    |

|    |               | Installing the Hardware                                      |    |

|    |               | After Restarting                                             |    |

|    | 2.4.1         |                                                              |    |

|    | 2.4.2         |                                                              |    |

|    | 2.4.3         |                                                              |    |

|    | 2.4.4         |                                                              |    |

|    | 2.4.5         |                                                              |    |

|    | 2.4.6         |                                                              |    |

|    | 2.5.          | LabVIEW RT                                                   |    |

|    |               | Distribution for Windows 95/98/2000/NT4/XP                   |    |

|    |               | Distribution for Linux                                       |    |

|    |               |                                                              |    |

| 3. | PRC           | DUCT DESCRIPTION                                             | 34 |

|    | 3.1.          | Overview                                                     | 34 |

|    | 3.2.          | Channel Input                                                | 36 |

|    | 3.2.1         |                                                              |    |

|    | 3.2.2         | . Input Protection                                           | 36 |

|    | 3.2.3         | ·                                                            |    |

|    | 3.2.4         | Bandwidth and Rise Time                                      | 36 |

|    | 3.2.5         | Input Voltage and Offset                                     | 36 |

|    | 3.2.6         | Vertical Resolution                                          | 37 |

|    | 3.2.7         | DC Accuracy                                                  | 37 |

|    | 3.3.          | Trigger                                                      | 37 |

|    | 3.3.1         | . Trigger Source                                             | 37 |

|    | 3.3.2         | Trigger Coupling                                             | 37 |

|    | 3.3.3         | 66                                                           |    |

|    | 3.3.4         | 00 - 1                                                       |    |

|    | 3.3.5         |                                                              |    |

|    | 3.3.6         | Trigger Status                                               | 38 |

# acqiris

| 3.3.7.   | Trigger Veto and Timeout (AP101/AP201 ONLY)             |    |

|----------|---------------------------------------------------------|----|

| 3.4. Dat | a Acquisition – Common                                  |    |

| 3.4.1.   | Timing                                                  |    |

| 3.4.2.   | Sampling Rate                                           |    |

| 3.5. Dat | a Acquisition - Digitizer Mode                          | 39 |

| 3.5.1.   | Acquisition Memory and Time Base Range - Digitizer Mode | 39 |

| 3.5.2.   | Pre- and Post-Trigger Delay - Digitizer Mode            | 40 |

| 3.5.3.   | Single and Sequence Acquisitions - Digitizer Mode       | 40 |

| 3.6. Dat | a Acquisition – Analyzer mode                           | 41 |

| 3.6.1.   | Random and Synchronized Triggers                        | 42 |

| 3.6.2.   | Time Base Range                                         |    |

| 3.6.3.   | Dual-Bank Memory & Buffered Sequence Acquisition        | 43 |

| 3.6.4.   | Buffered Acquisition Mode with Data Readout             |    |

| 3.7. AP  | 235/AP240 Data processing                               |    |

| 3.7.1.   | User Gates                                              |    |

| 3.7.2.   | Threshold gates                                         |    |

| 3.7.3.   | Time stamp information                                  |    |

| 3.7.4.   | Peak detection.                                         |    |

| 3.7.5.   | Interpolation of Peak Position and Amplitude            |    |

| 3.7.6.   | Histogramming Peak Data                                 |    |

|          | 101/AP201 Data processing                               |    |

| 3.8.1.   | User Gates                                              |    |

| 3.8.2.   | Simple peak detection                                   |    |

| 3.8.3.   | Peak detection with Hysteresis                          |    |

| 3.8.4.   | Peak Interpolation                                      |    |

|          | ernal Clock and Reference                               |    |

|          | nt Panel Inputs and Controls                            |    |

|          | ernal Calibration.                                      |    |

|          |                                                         |    |

|          | ctrical, Environmental and Physical Specifications      |    |

| 3.12.1.  |                                                         |    |

| 3.12.2.  | Environmental and Physical                              |    |

|          | NG THE AP_SSRDEMO APPLICATION                           |    |

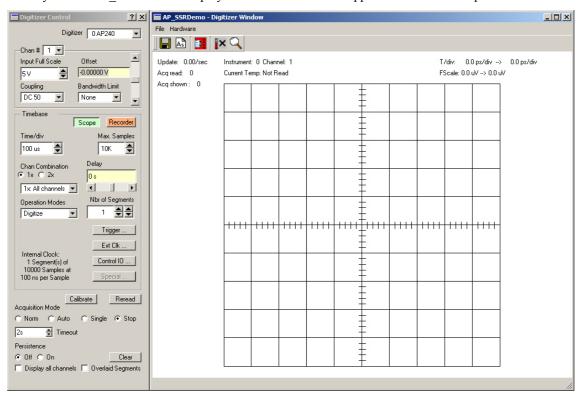

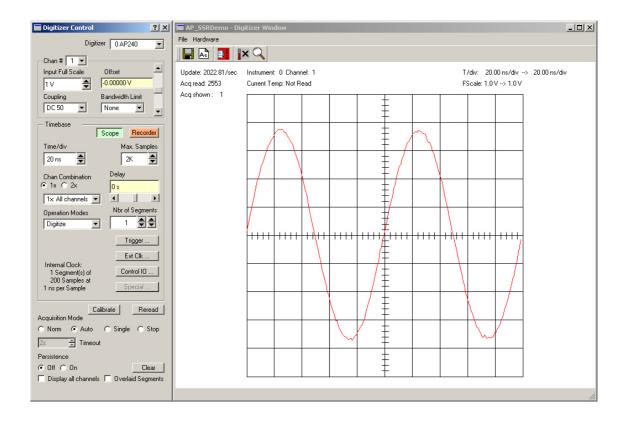

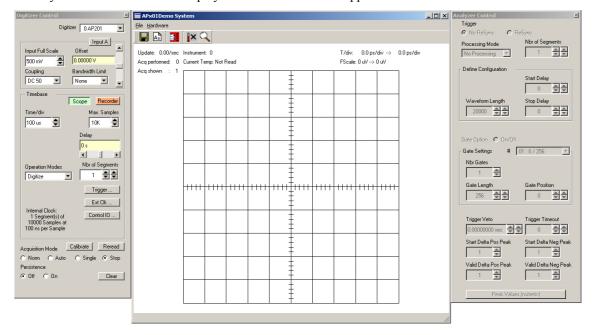

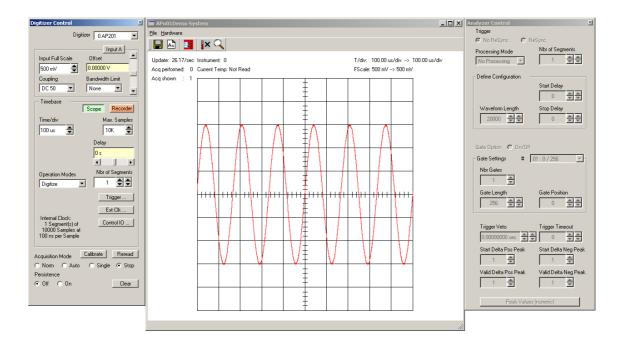

| 4.1. Get | ting Started with AP_SSRDemo                            | 50 |

| 4.2. Edi | ting Fields                                             | 51 |

| 4.3. Dig | ritizer Control Panel and Functions                     | 51 |

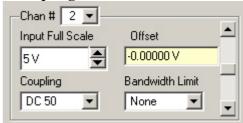

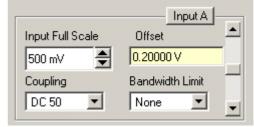

| 4.3.1.   | Input Voltage Scale, Offset, Coupling and Bandwidth     | 52 |

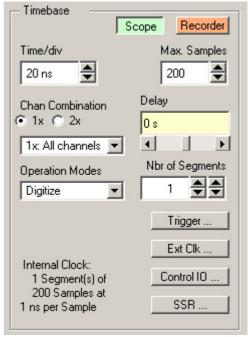

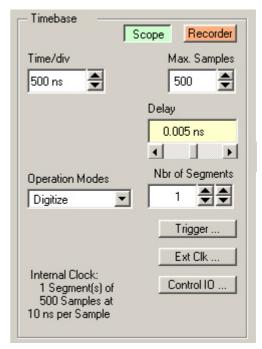

| 4.3.2.   | Digitizer Timebase and more                             | 52 |

| 4.3.3.   | Operation Mode                                          | 53 |

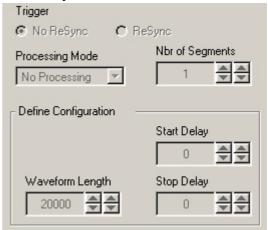

| 4.3.4.   | Trigger                                                 | 53 |

| 4.3.5.   | External Clock                                          | 53 |

| 4.3.6.   | Control IO Settings                                     | 53 |

| 4.3.7.   | Acquisition Mode                                        | 53 |

| 4.3.8.   | Display options                                         | 54 |

| 4.4. An  | alyzer Control Panel and Functions                      | 54 |

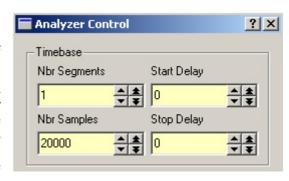

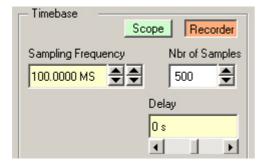

| 4.4.1.   | Analyzer Timebase and Memory                            | 54 |

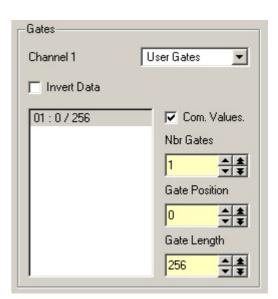

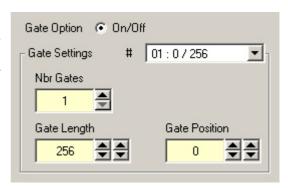

| 4.4.2.   | User Gate definition                                    |    |

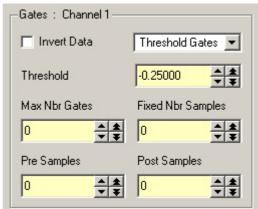

| 4.4.3.   | Threshold Gate definition                               | 55 |

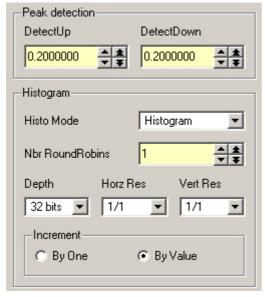

| 4.4.4.   | AdvancedTDC mode Peak and Histogram definition          |    |

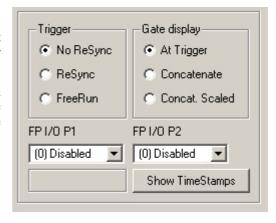

| 4.4.5.   | Additional Controls & Time Stamp data                   |    |

| 4.4.6.   | Waveform storage                                        | 56 |

| 4.4.7.   | Control panel reactivation                              |    |

| 4.4.8.   | Temperature display                                     | 56 |

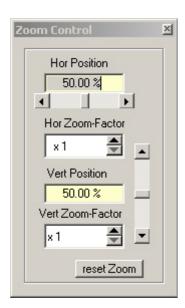

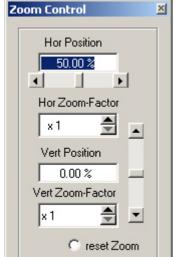

| 4.4.9.   | Zoom display control                                    | 56 |

| 5 DIINNI | NC THE ADVAIDEMA ADDITION                               | 50 |

# acqiris

| 5.1.  | Getting Started with APx01Demo                           | 58    |

|-------|----------------------------------------------------------|-------|

| 5.2.  | Editing Fields                                           | 59    |

| 5.3.  | Digitizer Control Panel and Functions                    | 59    |

| 5.3   | 3.1. Input Voltage Scale, Offset, Coupling and Bandwidth | 60    |

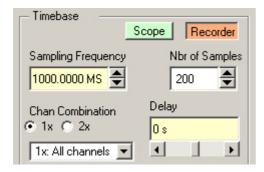

| 5.3   | 3.2. Digitizer Timebase and more                         |       |

| 5.3   | 3.3. Trigger                                             | 61    |

| 5.3   | 3.4. Acquisition Mode                                    |       |

| 5.3   | 3.5. Persistence display                                 | 62    |

| 5.4.  | Analyzer Control Panel and Functions                     | 62    |

| 5.4   | 4.1. Analyzer Timebase and Memory                        | 62    |

| 5.4   | 4.2. Gate definition                                     | 62    |

| 5.4   | 4.3. Trigger Veto and Timeout                            | 62    |

| 5.4   | 4.4. Hysteresis Mode Peak Parameters                     | 63    |

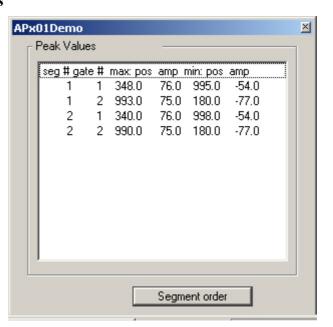

| 5.4   | 4.5. Display of Peaks                                    | 63    |

| 5.5.  | Display Window Functions                                 | 63    |

| 5.5   | 5.1. Waveform storage                                    | 63    |

| 5.5   | 5.2. Control panel reactivation                          | 64    |

| 5.5   | 5.3. Temperature display                                 | 64    |

| 5.5   | 5.4. Zoom display control                                | 64    |

| 6. AP | PPENDIX A: XA100 BNC INPUT OVERVOLTAGE PROTECTION        | V65   |

| 7. AP | PPENDIX B: XP102 FAN UNIT FOR THE AP FAMILY OF MODU      | LES66 |

#### 1. Out of the Box

#### 1.1. Message to the User

Congratulations on having purchased an Acqiris data conversion product. Acqiris Digitizers/Analyzers are high-speed data acquisition modules designed for capturing high frequency electronic signals. To get the most out of the products we recommend that you read this manual carefully. We trust the product you have purchased will meet with your expectations and provide you with a high quality solution to your data conversion applications.

## 1.2. Using this Manual

This guide assumes you are familiar with the operation of a personal computer (PC) running a Windows 95/98/2000/NT4/XP or other supported operating system. It also assumes you have a basic understanding of the principles of data acquisition using either a waveform digitizer or a digital oscilloscope.

The manual is divided into 5 separate sections. To understand the elements of operation for the module it is essential that you read them as appropriate.

Chapter 1 **OUT OF THE BOX**, describes what to do when you first receive your new Acqiris product. Special attention should be paid to sections on safety, packaging and product handling. Before installing your product please ensure that your system configuration matches or exceeds the requirements specified.

Chapter 2 *INSTALLATION*, covers all elements of installation and performance verification. Before attempting to use your Acqiris product for actual measurements we strongly recommend that you read all sections of this chapter.

Chapter 3 **PRODUCT DESCRIPTION**, provides a full description of all the functional elements of the Analyzer.

Chapter 4 **RUNNING THE AP\_SSRDEMO APPLICATION**, describes the operation of an application that enables basic operation of Acqiris AP235/AP240 digitizers and analyzers in a Windows 95/98/2000/NT4/XP environment.

Chapter 5 **RUNNING THE APX01DEMO APPLICATION**, describes the operation of an application that enables basic operation of Acqiris AP101/AP201 digitizers and analyzers in a Windows 95/98/2000/NT4/XP environment

For information necessary for writing you own software to control Acqiris products you should refer to the **Programmer's Guide** and the **Programmer's Reference Manual**.

#### 1.3. Conventions Used in This Manual

The following conventions are used in this manual:

This icon to the left of text warns that an important point must be observed.

**WARNING** Denotes a warning, which advises you of precautions to take to avoid being electrically

shocked.

**CAUTION** Denotes a caution, which advises you of precautions to take to avoid electrical,

mechanical, or operational damages.

**NOTE** Denotes a note, which alerts you to important information.

*Italic* text denotes a warning, caution, or note.

**Bold Italic** text is used to emphasize an important point in the text or a note

mono text is used for sections of code, programming examples and operating system

commands.

#### 1.4. Disclaimer and Safety

The AP Series PCI Analyzer cards have been designed to operate in a standard PCI slot found inside most personal computers. Power for the modules is provided by plugging them into a free slot (refer to the installation procedure).

$\Lambda$

**CAUTION:**

Do not exceed the maximum input voltage rating! The maximum input voltage for 50  $\Omega$  input impedance is  $\pm 5$  V.

#### 1.5. Warning Regarding Medical Use

The AP Series PCI Analyzer cards are not designed with components and testing intended to ensure a level of reliability suitable for use in treatment and diagnosis of humans. Applications of these cards involving medical or clinical treatment can create a potential for accidental injury caused by product failure, or by errors on the part of the user. These cards are *not* intended to be a substitute for any form of established process or equipment used to monitor or safeguard human health and safety in medical treatment.

WARNING:

The modules discussed in this manual have not been designed for making direct measurements on the human body. Users who connect an Acqiris module to a human body do so at their own risk.

#### 1.6. Packaging and Handling

Your Analyzer is shipped with the following components:

- A compact disc that includes

- 7 product user manuals in electronic form (Family of 8-bit Digitizers, Family of 10-bit Digitizers, Family of 12-bit Digitizers, Family of Averagers, Family of Analyzers, CC10X Family of CompactPCI Crates and CC121 CompactPCI Crate),

- o 1 Programmer's Guide and 1 Programmer's Reference Manual,

- o device drivers with sample software for different operating systems, environments and languages,

- the AcqirisLive application, a demonstration program for our digitizer and averager products,

- the AP\_SSRDemo application, a demonstration program for the Acqiris AP235/AP240 Analyzers,

- o the APx01Demo application, a demonstration program for the Acqiris AP101/AP201 Analyzers,

- o product data sheets,

- o full installation procedures for use with Microsoft Windows, National Instruments LabVIEW RT, Phar Lap ETS, Wind River VxWorks, and Linux software.

- A declaration of conformity

- Optional documentation such as a model-dependent document giving Specifications & Characteristics, a Calibration Certificate, or a Performance Verification

After carefully unpacking all items, inspect each to ensure there are no signs of visible damage. Also check that all the components received match those listed on the enclosed packing list. Acqiris cannot accept responsibility for missing items unless we are notified promptly of any discrepancies. If any items are found to be missing or are received in a damaged condition please contact the Customer Support Center or your local supplier immediately. Retain the box and packing materials for possible inspection and/or reshipment.

#### 1.7. Warranty

All Acqiris Analyzer products are warranted to operate within specification, assuming normal operation, for a period of three years from the date of shipment. It is recommended that yearly calibration be made in order to verify product performance. All repairs, replacement and spare parts are warranted for a period of 3 months. A 5-year repair warranty is available as an option.

Acqiris endeavors to provide leading edge technology that includes the latest concepts in hardware and software design. As such software and firmware used with the products is under continual refinement and improvement. All software and instrument firmware is supplied "as is" with no warranty of any kind. Software and firmware is thoroughly tested and thought to be functional at the time of shipment. At Acqiris' discretion software and firmware may be revised if a significant operational malfunction is detected.

Products supplied but not manufactured by Acqiris are covered solely by the warranty of the original equipment manufacturer.

In exercising this warranty, Acqiris will repair or replace any product returned to the Customer Support Center, or an Authorized Repair Center, within the warranty period. The warranty covers all defects that are a result of workmanship or materials. This excludes defects that are caused by accident, misuse, neglect, or abnormal operation.

The purchaser is responsible for returning the goods to the nearest Customer Support Center. This includes transportation costs and insurance. Acqiris will return all warranty repairs with transportation prepaid.

#### 1.8. Warranty and Repair Return Procedure, Assistance and Support

Before returning any Acqiris product for repair please contact your nearest service center for a Return Authorization Number (RAN). In order to issue a RAN we suggest that you communicate with us using eMail. Our standard form will require your name, company, phone number and address, the model and serial numbers of the unit to be repaired and a brief description of the problem. If a unit returned under guarantee is found to be working normally and this procedure was not followed we reserve the right to charge you for the work done.

As well as providing you with an RAN, Acqiris Support Centers can assist you with any questions concerning the installation, operation or service of your equipment. For your nearest customer support center contact Acqiris at 1-877-ACQIRIS in the USA, +41 22 884 33 90 in Europe or +61 3 9888 4586 in the Asia-Pacific region.

#### 1.9. System Requirements

In order to obtain reasonable performance from your instrument the following minimum PC System Requirements should be respected:

**Processor:** 150 MHz Pentium (higher recommended)

**Memory:** 64 Mbytes RAM. The previous number is a very rough estimate. Assuming that you are using AcqirisLive or an application of your own that operates on the acquired data it seems reasonable to ask for 10 times the total acquisition memory that you will be using at the same time in the application. Performance is likely to be degraded if less memory is available.

**Display resolution:** At least 800 x 600 pixels and 256 colors for use of the Acqiris demo programs.

Operating System: Microsoft Windows 95/98/2000/NT4/XP, Phar Lap Real-time ETS 12.0 Kernel, Wind River VxWorks 5.5.1, and Linux (RedHat 8.0 - Kernel Version 2.4.18, RedHat 9.0 - Kernel Version 2.4.20, or Fedora Core 3 - Kernel Version 2.6, Debian Sarge 2.6.8). Linux kernel driver source code is available for compilation.

Hard Drive Space: 20 Mbytes Minimum

**CD Drive:** (or any method to copy Acqiris Software installation files from CD to the hard drive such as LAN, floppy drive, etc.)

ETS: The example files are for Microsoft Visual Studio 6.0 with Phar Lap ETS 12.0 support.

**LabVIEW:** The Acqiris LabVIEW driver is available for National Instruments LabVIEW versions 6.0, 6.1, 7.0, or 7.1

**LabVIEW RT:** The Acqiris LabVIEW RT driver is available for National Instruments LabVIEW RT version 7.1 or higher. The VISA driver must be version 3.0 or higher.

**MATLAB:** The Acqiris MEX interface can be used with MathWorks MATLAB 6.5 or a newer vesion. Alternatively, to successfully use the Acqiris MATLAB Adaptor you must have at least MathWorks MATLAB 6.5 with the Data Acquisition Toolbox.

**Visual BASIC:** The interface files and examples are available for Microsoft Visual Basic versions 5 or 6 and the interface files only for .NET.

Tornado: The example files are useable with Wind River Tornado 2.2.1

#### 1.10. Transport & Shipping

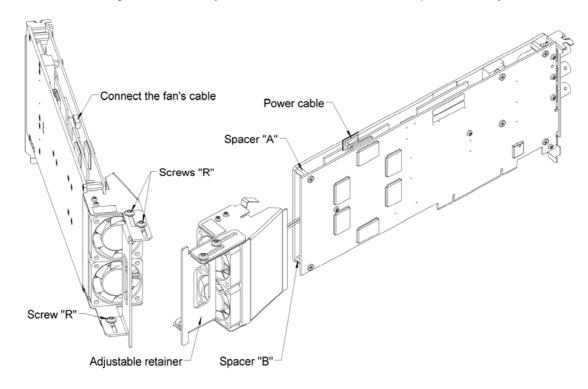

CAUTION: Cards can be safely transported in their original shipping packages. The transport of AP cards mounted in a PC is a more delicate issue. Because of their mass the cards can vibrate loose unless they are properly secured and braced. However, properly mounted AP cards with XP102 fans can be sufficiently well held; the Adjustable retainer must be used so as to hold the card in place.

#### 1.11. Maintenance

The cards do not require any maintenance. There are no user serviceable parts inside. A periodic calibration can be obtained on request.

# 1.12. Cleaning

Cleaning procedures consist only of exterior cleaning.

Clean the exterior surfaces of the module with a dry lint-free cloth or a soft-bristle brush. If any dirt remains, wipe with a cloth moistened in a mild soap solution. Remove any soap residue by wiping with a cloth moistened with clear water. Do not use abrasive compounds on any parts.

## 1.13. Disposal and Recycling

Electronic equipment should be properly disposed of. Acqiris Analysers/Digitizers and their accessories must not be thrown out as normal waste. Separate collection is appropriate and may be required by law.

#### 2. **Installation**

This chapter describes how to install the Acqiris hardware and software for Windows 95/98/2000/NT4/XP, National Instruments LabVIEW RT, Linux, Phar Lap ETS, or Wind River VxWorks.

NOTE: For a first time installation Acqiris strongly recommends installing the software before inserting the hardware into the PC.

#### 2.1. **Installing the Software under Windows**

#### 2.1.1. Warnings

If Setup detects a previous installation of Acqiris software on your system, a warning screen will be displayed. It is recommended to exit Setup and uninstall older versions.

The installer from software releases prior to **Acgiris Software 2.0** installed the Digitizer Driver DLL files into the System directory. These will be removed by Setup. If you wish to keep the old installation on your system, you should exit Setup, and move all Acqiris driver files (acqiris\*, acqrs\* and acqir\*) to some archive directory.

The DLL files will be installed into the bin subdirectory of the Acqiris software root, and the corresponding path will be added to the PATH environment variable.

#### 2.1.2. Multiple Versions

With the software installation from Acqiris Software 2.0 (or above), it is possible to keep multiple versions on the same system, but you must specify a different root directory (i.e. Install Folder). If you keep the same directory, Setup will overwrite your previous installation.

To go back to a previous version, you must change the PATH environment variable and reinstall the Kernel driver:

- Under Windows 95/98.

- 1. Copy the VXD file from <old\_AcqirisSoftware\_root>\bin\kernel to the Windows\System directory.

- 2. Change the AcqirisDxRoot environment variable to the old root.

- 3. Reboot the computer.

- Under Windows 2000/NT4/XP,

- 1. Copy the SYS file from <old\_AcqirisSoftware\_root>\bin\kernel to the Windows\System32\drivers directory.

- 2. Change the AcqirisDxRoot, AcqirisDxDir and PATH environment variables to the old root.

- 3. Reboot the computer.

#### 2.1.3. Installation

Before installing the Acqiris hardware, you should complete the following steps to install the software for Windows 95/98/2000/NT4/XP.

NOTE: You will need administrator privileges to complete the software installation under Windows 2000/NT4/XP.

- 1. Insert the Acqiris Software CD into the CD-ROM drive of your computer. If the Autorun program does not start automatically (Autoplay disabled), you can start it manually, or navigate to the AcqirisSoftware\Windows folder in order to display the files included.

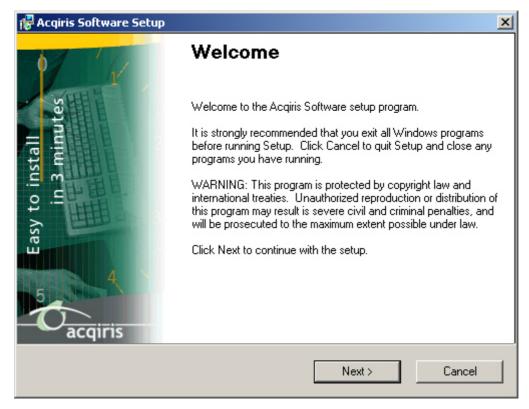

- 2. Choose Install AcqirisSoftware for Windows95/98/NT4/2000/XP (or run Setup.exe from the AcqirisSoftware\Windows folder). After several seconds for initialization the following screen will appear.

3. To proceed with the installation click "Next". The following screen will be shown.

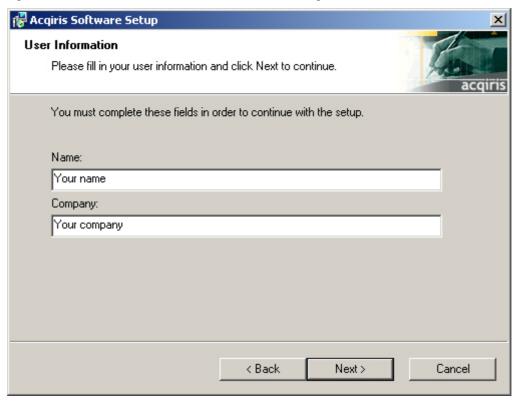

4. Please enter your user information and click "Next" to continue. If the program finds that there is still Acqiris software installed on your machine a warning panel (not shown) will appear. Otherwise, the next screen shows:

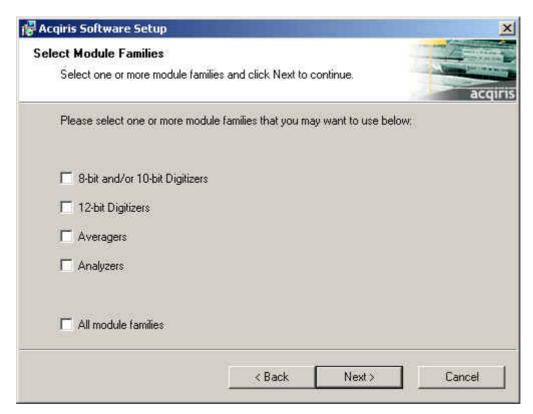

5. Pick the desired combination of module families and click "Next" to continue.

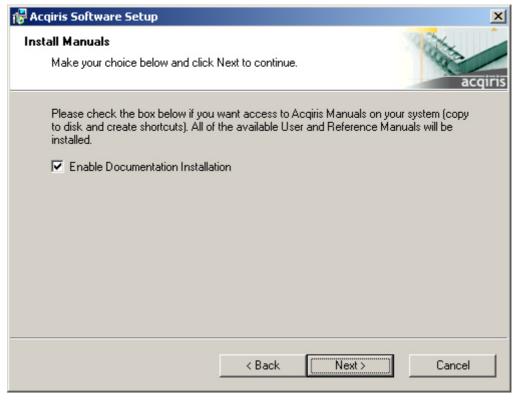

- 6. The screen above will normally allow the documentation to be installed. Remove the check from the box if you do not want online access to the manuals.

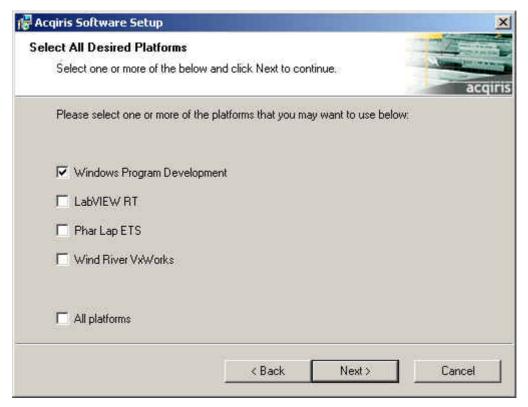

- 7. The next screen allows you to enable LabVIEW RT, Phar Lap ETS, and/or Wind River VxWorks support. By default there will be none but if desired you can install any of them together with Windows support or without Windows support. Click "Next" to continue.

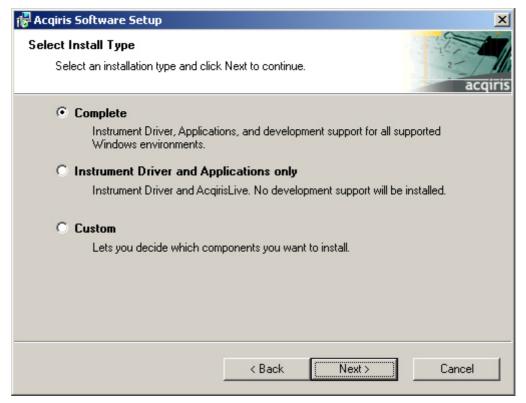

The screen below asks for the desired installation type. After having made your choice Click "Next" to continue.

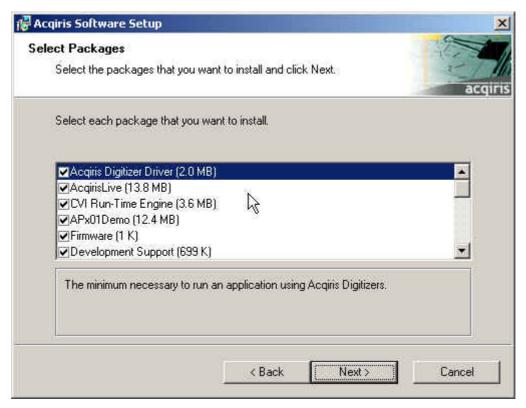

9. If you chose the Custom installation, the following screen will let you select each package individually. Note that the space indicated for LabVIEW, Firmware and UserManual packages is incorrect. The correct values are 10 MB, 23 MB, and 27 MB respectively.

- 10. If MATLAB is installed on your machine, you will be asked to point the installer to the MATLAB root directory. You should do this if you want the installer to modify the standard startup.m file to incorporate the Acqiris adaptor.

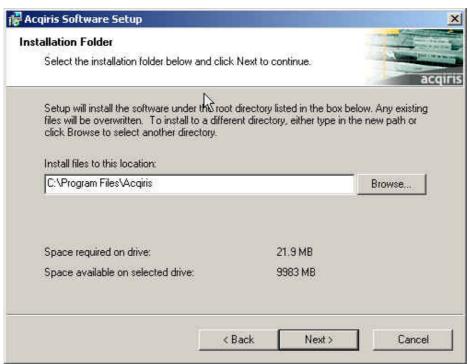

- 11. Now that the elements of the installation have all been decided you will be prompted for the installation folder. This will be the root directory of the Acqiris software installation. If User Manuals (27 MB) and Firmware (23 MB) are loaded more space than indicated here will be required on the drive. For the case of a Tornado 2.2 installation the folder name should not contain any spaces.

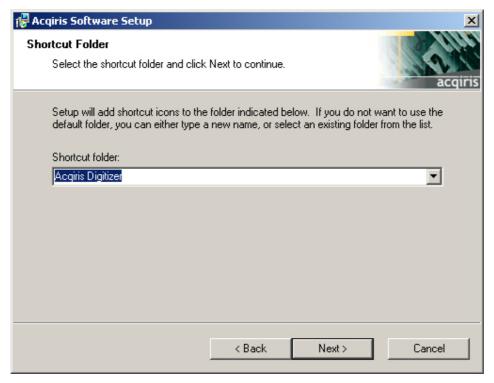

12. Furthermore, you should give a name to the shortcut folder. This is the menu entry under **Start** → Programs where you will find the shortcuts for AcqirisLive, manual(s), etc.

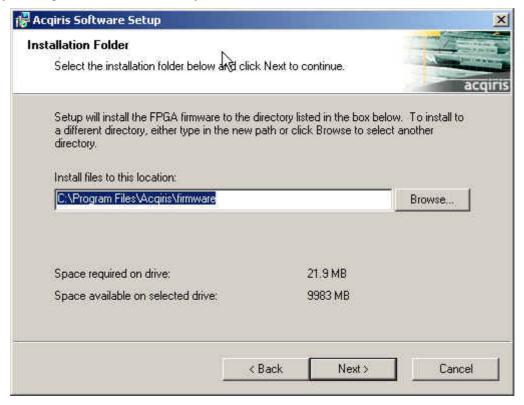

13. If you have enabled the installation of 12-bit Digitizers, Averagers, or Analyzers, the next screen lets you change the name of the directory where the FPGA firmware will be installed.

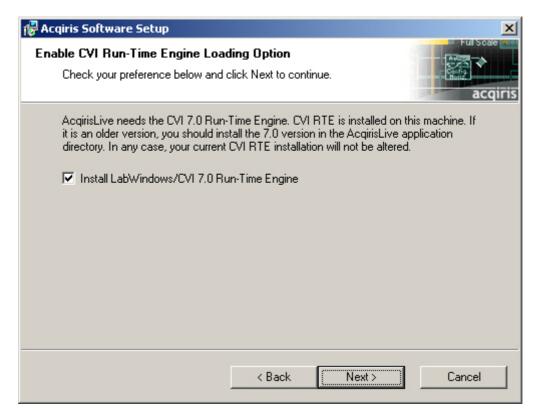

14. AcqirisLive needs the LabWindows/CVI 7.0 Run-Time Engine to run. If Setup has detected that a LabWindows/CVI Run-Time Engine is already installed on your system, it will ask you if you would like to install it locally for AcqirisLive anyway. If you are not sure about the version of the CVI Run-Time Engine on your system, it is recommended to install it locally. Click "Next" to continue.

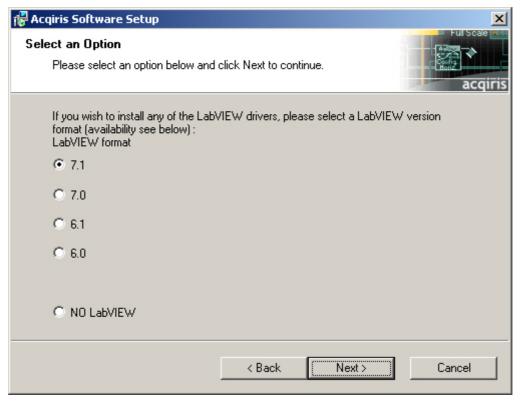

15. Depending on the install type, you may be asked which LabVIEW version format you want for the LabVIEW files. Select the appropriate format and click "Next" to continue.

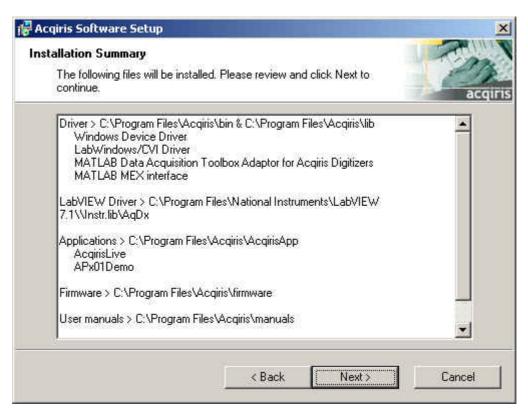

5. A summary will be shown to allow you to check what you have asked for

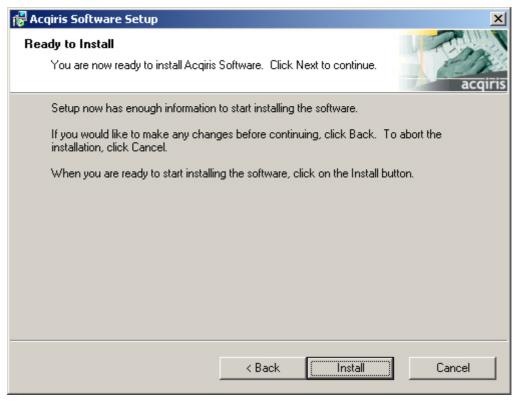

16. You are now ready to install. You may still go back to any previous screen to modify your selection. Click "Install" when ready.

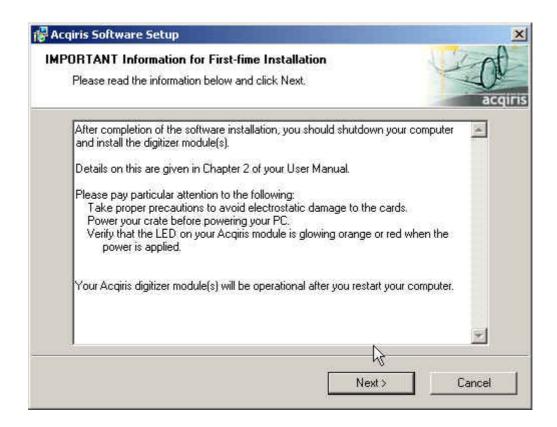

17. Setup will now copy the files and make the necessary changes to your system. When done, an information screen will be displayed. Please read this carefully.

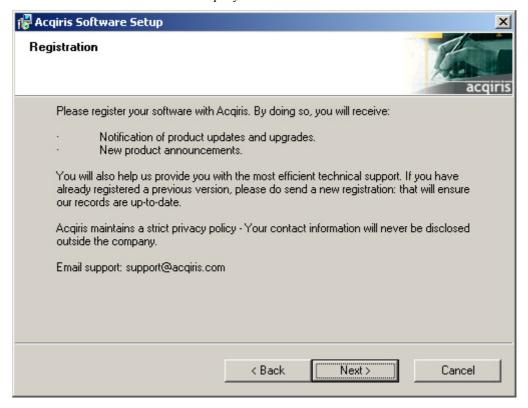

18. Registration of your installation will help us provide you with better support. You will also be notified of updates and upgrades. All information submitted to Acqiris will be treated confidentially and never be disclosed outside the company.

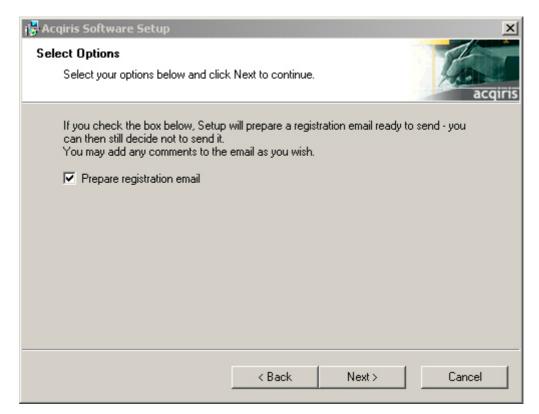

19. Setup will prepare a registration e-mail in your e-mail client application upon termination of the setup procedure. You can then decide whether or not you wish to send it. You may also add comments. Uncheck the box if you do not want to register your installation.

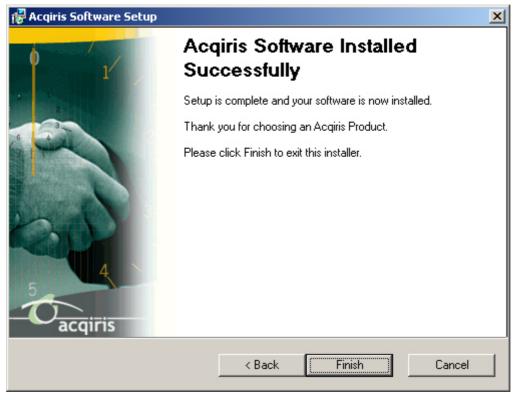

- 20. Click "Finish". The software installation is now complete.

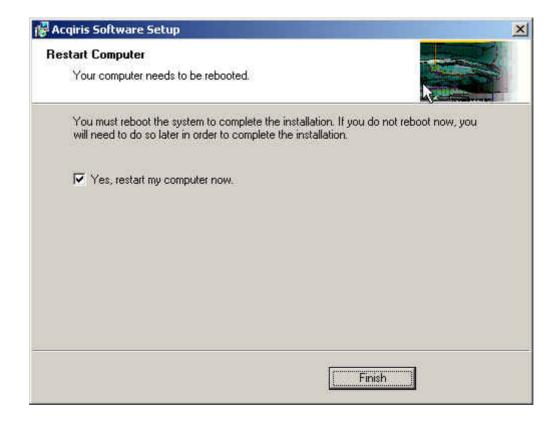

- 21. You can now either accept the suggestion to restart the computer or you should shutdown your computer and proceed with the hardware installation.

# 2.2. Installing the Software for Linux

The Acqiris Software is ready to install and run on Linux systems with either RedHat versions 8.0 (Kernel Version 2.4.18-14) or 9.0 (Kernel Version 2.4.20-8), Fedora Core 3 (Kernel Version 2.6.9-1.667 and 2.6.9-1.667smp), or Debian Sarge (Kernel Version 2.6.8-2-686). The driver and the library were compiled with GNU gcc 3.3. The Kernel Driver source code is available for recompilation for users with other Linux systems.

The tar file **AcqirisLinux.tar.bz2** should be copied to a local directory (e.g. your home directory) and then unpacked by using the following command

```

tar xjf AcqirisLinux.tar.bz2

```

The resulting directory **AcqirisLinux** contains an install script **drv-install** and a graphical Demo program **demo/AcqirisDemo**.

Before installing the driver you have to put the correct version of the Kernel mode driver into acqirisPCI.o. By default the version 2.4.18 RH8 is ready. If this is not what is needed type

```

cp lib/modules/acqrsPCI.o[.n] lib/modules/acqrsPCI.o

```

where the driver is from the following list

| acqrsPCI.o.2.4.18-14       | for Kernel Version 2.4.18 and RH8              |

|----------------------------|------------------------------------------------|

| acqrsPCI.o.2.4.20-8        | for Kernel Version 2.4.20 and RH9              |

| acqrsPCI.o.2.4.21-4.EL     | Red Hat Enterprise Linux version 3             |

| acqrsPCI.o.2.4.21-4.ELsmp  | for above with SMP                             |

| acqrsPCI.o.2.6.9-1.667     | for Kernel Version 2.6.9 and the Fedora Core 3 |

| acqrsPCI.ko.2.6.9-1.667smp | for above with SMP                             |

| acgrsPCI.ko 2.6.8-2-686    | for Debian Sarge                               |

To install the driver and the load script to the system, you have to get super user privileges and execute the driver install script by typing,

```

cd AcqirisLinux

./drv-install add

```

You can check that the driver is loaded properly with **1smod** or **dmesg**. The **drv-install** script has the following additional functionality:

dry-install rem to remove the driver and load script

**dry-install res** to restart the driver

If you intend to use an Averager, an Analyzer, or a 12-Bit Digitizer you must install the Firmware .bit files. You can either copy them from the Firmware directory of the CD-ROM or download them from our WEB site. They should be placed in the Firmware subdirectory of AcqirisLinux. In the case of the CD-ROM, this can be done by continuing the above command sequence with the following:

cp /mnt/CDRom/Firmware/\*.bit Firmware/

### 2.2.1. Kernel Mode Driver Compilation

For some special kernels, for example SMP, the kernel mode driver will have to be recompiled on the target system. All files needed to compile a new kernel mode driver are in AcqirisLinux/linuxdriverpci for Kernel 2.4 or in AcqirisLinux/linux2.6driverpci for Kernel 2.6

The makefile can be used for compilation under a Redhat compatible distribution. To compile the driver, the kernel header files need to be installed. The path variable INCLUDEDIR in the Makefile has to point to the correct kernel header files. The default path INCLUDEDIR = /usr/src/linux-2.4 or /usr/src/linux-2.6, respectively. This path usually is a link to the actual header files (driver source).

To compile for a new kernel under **linux-2.4**, issue the following commands:

- cd linuxdriverpci

- make clean to remove all \*.o files in AcqirisLinux/linuxdriverpci.

- make to generate a new kernel mode driver acqrsPCI.o and also copy it to the directory AcqirisLinux/lib/modules where the install script (drv install) can access it.

- drv\_install rem to remove the previous installed kernel mode driver.

- **dry install add** to install the new driver.

To compile for a new kernel under **linux-2.6**, issue the following commands:

- cd linux2.6driverpci

- make clean all to generate a new kernel mode driver acqrsPCI.ko from scratch.

- **make install** to copy the kernel module where it should reside.

Note that this version of the loadable kernel module had been tested on Linux kernel versions up to 2.6.13.

#### 2.2.2. Special cases

If you are running a Linux distribution that doesn't use the standard paths for the load scripts, you can load the driver with the command

```

cd AcqirisLinux

./drv-install load

```

Copy the driver to the module directory as follows:

```

cp lib/modules/acqrsPCI.o[.n] /lib/modules/{kv}/ACQIRIS/acqrsPCI.o

```

where [.n] is the optional designation of the desired version of the acqrsPCI driver as given above and {kv} is the appropriate system kernel version (i.e. 2.4.20).

Then add the following command to rc.local.

/sbin/insmod -f /lib/modules//{kv}/ACQIRIS/acqrsPCI.o

#### 2.2.3. Environment variables for the Firmware

Automatic loading of the firmware needed by 12-bit and AP modules relies on the environment variable AcqirisDxDir pointing to the directory containing the file AqDrv4.ini which in turn points to the directory containing the Firmware .bit files. Therefore, assuming that your Firmware is in /usr/local/AcqirisLinux/Firmware and that AqDrv4.ini is in /usr/local/AcqirisLinux/demo then you must edit AqDrv4.ini so that it contains the line

fpgaPath=/usr/local/AcqirisLinux/Firmware

Then, if your shell is csh or tcsh modify the /etc/csh.login file to contain the line

setenv AcqirisDxDir /usr/local/AcqirisLinux/demo

or, if your shell is bash, ksh, zsh or sh, modify the /etc/profile file to contain the lines

AcqirisDxDir=/usr/local/AcqirisLinux/demo export AcqirisDxDir

## 2.3. Installing the Hardware

1. Turn off the power of the PC.

**CAUTION:** Touch the antistatic package to a grounded metal part of the PC or crate before removing the card from the package. Electrostatic discharge can damage the card.

- 2. Open the PC, identify a free PCI slot and carefully insert the AP Series card into it. Be sure to ground yourself by touching the grounded PC frame and avoid touching any components on the AP Series card. Make sure that the grounding of the card's mounting bracket to the back panel rail of the computer is done correctly. Make sure that the fan's adjustable retainer is correctly positioned and tightened for mechanical support. Close the PC.

- 3. Turn on the power of the PC and start the operating system.

**NOTE:** Acqiris Analyzers are equipped with a LED. If this LED is not glowing orange or red when the power is applied there is a severe problem. Either the module is broken or the necessary voltages for its use are not available.

4. For **Windows NT/98/95 ONLY**: Go into the *BIOS Setup* menu. Under the *Advanced* section or the *Boot* section you may find a selection named Plug & Play OS. Check that its value is [No]. If it is not you should change it to this value and save the settings.

**NOTE:** For proper system operation under Windows NT/98/95 ONLY, the Acqiris Driver expects that the BIOS has already configured any modules present. Plug & Play OS [Yes] inhibits this activity and can result in the Acqiris hardware not being recognized.

5. Devices that were installed using a previous version of **Acqiris Software** the instruments in these logical positions will still appear as *Unknown Devices*. This can be changed to the new Acqiris type category with the Grey Diamond icon by **Uninstalling** the device and then **Installing** again. Instructions on this procedure can be found in the **ReadMe.txt** file in the **manuals** folder of your Acqiris Software installation.

## 2.4. After Restarting

#### 2.4.1. Windows 95

Under Windows95, the first time the system is started, the Plug&Play system will automatically detect the Acqiris hardware and briefly display a **New Hardware Found** dialog box prior to automatically installing the new hardware.

#### **2.4.2.** Windows 98

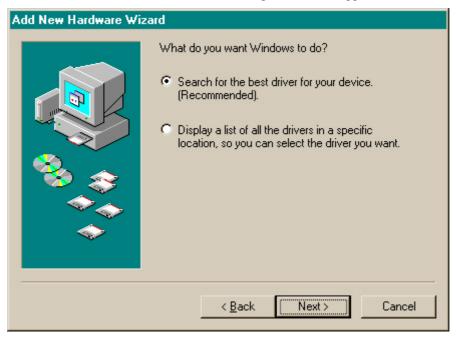

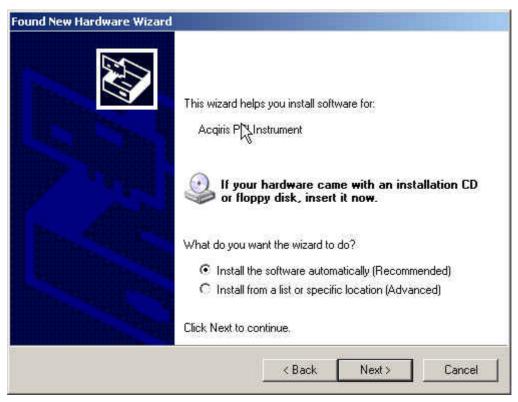

Under Windows98, the first time the system is started, the Plug&Play system will automatically detect the Acqiris hardware, briefly display a **New Hardware Found** dialog box and start the "Add New Hardware Wizard" displaying the window shown below.

To proceed with the installation click "Next". The following window will appear.

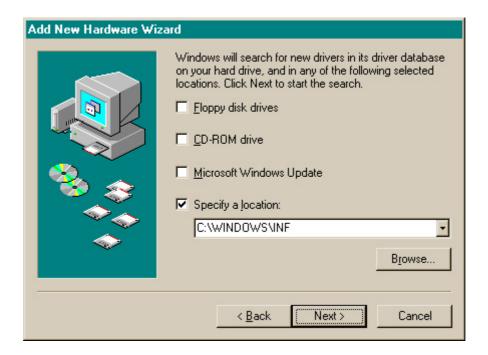

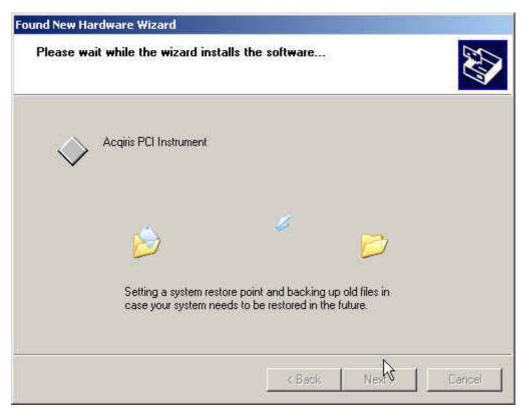

To proceed with the installation click "Next". The following window will appear.

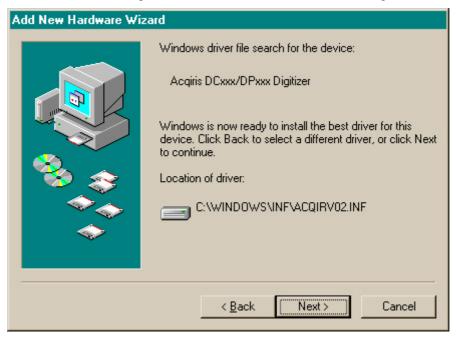

To proceed with the installation, keep the defaults and click "Next". The following window will appear.

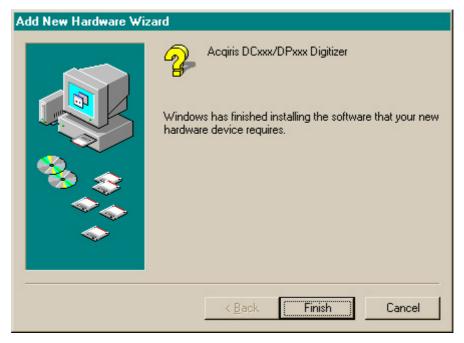

To proceed with the installation click "Next". The following window will appear.

Click "Finish" and the hardware installation will be complete.

#### 2.4.3. Windows 2000

Under Windows 2000, you *must* login with administrator privileges after the first boot following the hardware installation; the Plug&Play system must have the appropriate privileges to be able to complete your hardware installation successfully. After a successful hardware installation, you will be able to use your Acqiris Digitizer(s) with normal privileges.

At the first boot following the hardware installation, Windows will detect the new hardware and will install the devices automatically. The following image will appear.

**NOTE:** In some systems an application program (such as AcqirisLive) will not yet work correctly at this point. One additional boot cycle may be needed if this is the first time that a hardware board is being installed.

#### 2.4.4. Windows XP

Under Windows XP, you *must* login with administrator privileges after the first boot following the hardware installation; the Plug&Play system must have the appropriate privileges to be able to complete your hardware installation successfully. After a successful hardware installation, you will be able to use your Acqiris Analyzer(s) with normal privileges.

If you login with administrator privileges after the first boot following the hardware installation, Windows will detect the new hardware and start the "Found New Hardware Wizard" after a few seconds.

**NOTE:** Acqiris Analyzers and the drivers provided do not support the **Standby** mode. You may want to de-activate this feature if it is in use on your PC. An error message will occur if the transition into **Standby** mode is attempted.

To proceed with the installation click "No, not this time" and then "Next". The following window will appear:

To proceed with the installation click "Next". You should then see

and then

**NOTE:** In some systems an application program (such as AcqirisLive) will not yet work correctly at this point. One additional boot cycle may be needed if this is the first time that a hardware board is being installed.

#### 2.4.5. Windows NT 4.0

Under Windows NT 4.0, the operating system does not automatically detect new hardware. However, the Acqiris device drivers are configured to automatically search for all Acqiris devices present on the system when the NT driver is started. Therefore the system is ready to run immediately after booting the computer.

#### **2.4.6.** MATLAB

If you want to use the Data Acquisition Toolbox interface then the Acqiris Adaptor has to be registered. This can be done with the following command:

```

>> Aq Install

```

This command will also generate diagnostic information that confirms that the installation succeeded. Since a calibration will be performed the command may take a while to execute. If no errors are shown the CallAcqiris.dll file was successfully installed. You should see messages like this:

```

Registering the Acqiris Adaptor... 'aq.dll' successfully registered.

AdaptorDllName: 'C:\Program Files\Acqiris\bin\aq.dll' Location

AdaptorDllVersion: '1, 2, 0, 1' DLL Version

AdaptorName: 'aq'

BoardNames: {'DP240[12767]'} Either Model[Serial Number]

or {Ixn cell}

InstalledBoardIds: {'0'} Board Identifiers for MATLAB

ObjectConstructorName: {'analoginput('aq','0')' ''' ''}

or {nx3 cell}

Help for CallAcqiris module

Syntax: CallAcqiris('FunctionName', ArgIn, ..., ArgOut, ...)

List of available functions from this module:

```

Followed by more help lines and the next command prompt.

If there is an error, please check your paths under MATLAB and contact us if needed.

#### 2.5. LabVIEW RT

The Acqiris Driver supports all Acqiris Instruments.

The Aq RT.inf and AqRT 4.ini files must be uploaded to the target. To do this,

- start the MAX application,

- right click on the target

- select file transfer

- select the Aq\_RT.inf file on your host machine and upload ('To Remote') to the LabVIEW RT working directory (/NI-RT/system) on the target

- select the Aq\_RT.ini file on your host machine and upload ('To Remote') to the LabVIEW RT working directory (/NI-RT/system) giving it the name AqDrv4.ini

For Acqiris modules which need FPGA files you should,

- create the folder \firmware in the /NI-RT/system directory using the file transfer application

- select the FPGA files (from <AcqirisDxRoot>\Firmware) you want to copy to the target and upload them into the firmware directory

Restart the target after finishing the file transfers.

Restart the MAX Explorer and you should have Acqiris Analyzers detected in your system.

#### 2.6. Distribution for Windows 95/98/2000/NT4/XP

After a complete installation of Acqiris Software for Windows (supports Windows 95/98/2000/NT4/XP), the following files and directories should exist in the chosen installation directory:

irunin.\* miscellaneous install files

- AcqirisApp directory:

AcqirisLive.exe AcqirisLive Windows application

AP\_SSRDemo.exe

APx01Demo.exe

APx01Demo application

GeoMapper.exe Acqiris GeoMapper application

viauto.dll NI software needed by AcqirisLive

virt.dll NI software needed by AcqirisLive

virte.dll NI software needed by AcqirisLive

dataskt.dll NI software needed by AcqirisLive

mesa.dll software needed by AcqirisLive

cvirte directory containing bin and fonts subdirectories

Data directory to be used for saved data files from AcgirisLive or APx01Demo

■ AqSC .\* files created only after 1<sup>st</sup> run

- **Bin** directory:

aq.dll software needed by MATLAB Adaptor

AqDrv4.dll Acqiris Windows Digitizer Driver DLL

• AqDrv4.fp CVI function panel: contains all the driver C-functions

• AqDrv4.ini Optionally created to indicate where FPGA .bit files can be found.

AqDrvMex.dll software needed by MATLAB MEX interface

AqISI3.dll software needed by AcquirisLive and MATLAB Adaptor

AqRT 4.dll software needed for LabVIEW RT

AqSCl3.dll software needed by AcqirisLive and MATLAB Adaptor

CallAcqiris.dll software needed by MATLAB Adaptor

FactoryInstrumentSettings.AqSettings MATLAB Instrument Settings Configuration file

msvcp71.dll Microsoft VC run-timemsvcr71.dll Microsoft VC run-time

qt-mt332.dll software needed by AcqirisLive and MATLAB Adaptor

qt-mt333.dll software needed by AcqirisLive and MATLAB Adaptor

- **Bin\kernel** directory (only the files needed for your OS will be present):

acqirv00.vxd Win9x low level driver

acqirv04.inf Win9x/2000 low level driver

Acqir400.sys WinNT4 low level driver

Acqir500.sys Win2000 low level driver

Aq\_RT.inf LabVIEW RT driver

**CVI** directory with the files needed for a LabWindows/CVI program:

• GetStarted.c C source code of CVI sample program

GetStarted.h Header associated with the User Interface file of CVI sample program

GetStarted.prj LabWindows/CVI project file of CVI sample program

GetStarted.uir

CVI User Interface file of CVI sample program

# acgiris

- ETS directory with the files need for a Phar Lap ETS sample program

GetStartedETS.cpp C source code of ETS sample program

GetStartedETS.dsp VisualC++ 6.0 project file of ETS sample program

GetStartedETS.dsw VisualC++ 6.0 workspace file of ETS sample program

(only after 1<sup>st</sup> run)

GetStartedETS.lnk ETS application linker file

GetStartedETS.rc VisualC++ 6.0 resource file of ETS sample program

GetStartedETS.vsb VisualSystemBuilderProject file of ETS sample program

• resource.h Header associated with the resources for the ETS sample program

■ **RTOS.ini** ETS Configuration file

- **Firmware** directory containing FPGA .bit files for AC210, AC240, AP100, AP101, AP200, AP201, AP235, AP240, DP306, DP308, DP310, DC436, DC438, DC440, SC210, and SC240.

- **Include** directory with:

• **AcgirisD1Import.h** Header file for C/C++

• Acqiris D1Interface.h Acqiris Device Driver Interface Definitions (API)

AcqirisDataTypes.h

Data Structure Header file for C/C++

AcqirisErrorCodes.h Acqiris Error Code definitions

AcqrsD1Interface.bas Header file for Visual Basic

AcqrsD1Interface.vb Header file for Visual Basic .NET

• visatype.h VISA types, already installed if you have LabWindows/CVI

• vpptype.h already installed if you have LabWindows/CVI

Lib directory with C/C++ link libraries for major compilers:

AqDrv4.lib default, Microsoft compiler

borland\AqDrv4.lib Borland compiler

msvc\AqDrv4.lib Microsoft compiler

AqETS4.lib Phar Lap ETS library

AqLibETS.lib Phar Lap ETS library

AqRT\_4.lib LabVIEW RT library

Manuals directory with:

AqDrv4.HLP C driver help

ProgrammersGuide.pdf

ProgrammersReferenceManual.pdf

• ReadMe.txt A user oriented ReadMe file with information about the

installed software

ShortCutNames.txt needed for (Un)Install

UserManual12BitDigitizers.pdf

UserManual10BitDigitizers.pdf

UserManual8BitDigitizers.pdf

UserManualAnalyzers.pdf

UserManualAveragers.pdf

UserManualCC10XCrates.pdf

UserManualCC121Crate.pdf

MATLAB directory with:

InstrumentSettings.AqSettings MATLAB Instrument Settings Configuration file

(only after 1<sup>st</sup> run)

Aq startup.m

example for use in Toolbox\local\Aq startup.m

# acgiris

daq\Aq install.m needed for registration and validation

daq\Aq\_ModeLive.m

daq\Aq\_MultipleAcquisition.m

daq\Aq\_SingleAcquisition.m

mex\Aq\_GetStarted.m

example

example

mex\help\Aq\_\*.m help files for all routines

- **ReplacedSystemFiles** directory with old versions for possible recovery (not for Windows XP):

- msvcp60.dll

- msvcrt.dll

- tornado directory with sample program:

- GetStartedVxW.cpp Source file for Tornado sample program

- GetStartedVxW.wpj

GetStartedVxW.wsp

Tornado Project file for Tornado sample program

Tornado Workspace for Tornado sample program

- **VB** directory with the files needed for either a 12-bit digitizer or 8-bit digitizer Visual Basic program:

- AcqirisShow12.frm Source code for main window of VB sample program

- AcqirisShow12.vbp Visual Basic project file of VB sample program

- AcqirisShow12.vbw

VBW file of VB sample program

- AcqirisShow8.frm Source code for main window of VB sample program

- AcqirisShow8.vbp Visual Basic project file of VB sample program

- AcqirisShow8.vbw

VBW file of VB sample program

- **DevCtrlForm12.frm** Source code for device control dialog box of VB sample program

- **DevCtrlForm8.frm** Source code for device control dialog box of VB sample program

- VC directory with the files needed for either an averager or a digitizer VisualC++ program:

- GetStartedAvgVC.cpp C++ source code of VC sample program

- **GetStartedAvgVC.dsp** VisualC++ 6.0 project file of VC sample program

- GetStartedVC.cpp C++ source code of VC sample program

- GetStartedVC.dsp VisualC++ 6.0 project file of VC sample program

- GetStartedVC.rc Resource file of VC sample program

resource.h Resource file of VC sample program

- **vxworks** directory with:

- AcqirisVxWUmode.out AcqrsD1 VxWorks driver

- VxWorksDriverPCI.out AcqrsD1 VxWorks Low Level driver

- **LabVIEW**\help directory with the help file needed for a LabVIEW program:

- AQDRV4.HLP

- LabVIEW\Instr.lib\AqDx directory with the files needed for the chosen LabVIEW version:

- acstat.mnu

- applic.mnu

- AqDx.llb

- AqDx\_obs.llb

- AqDx u.llb

- AqRT.llb

- AqRT\_u.llb

- config.mnu

- data.mnu

- dir.mnu

- util.mnu

- "Windows" directory (Windows or WINNT)

- Acqiris Software Setup Log.txt a readable record of installation activity

- "Windows system" directory (Windows\system or WINNT\system32)

acqirv00.vxd Win9xdrivers\Acqir400.sys NT4

drivers\Acqir500.sys

msvcp60.dll

Msvcrt.dll

Microsoft VC run-time

Microsoft VC run-time

"Windows" \Inf directory (WINNT\Inf)acqirv04.inf Win9x/2000

#### 2.7. Distribution for Linux

- AcqirisLinux directory:

drv-install install script, creates system load script

acqstartstop hidden file used by the install script

demo directory:

AcqirisDemo script to start the AcqirisDemo application

AcqirisDemo.bin AcqirisDemo application, based on the Qt GUI

■ **libqt-mt.so.3** Qt 3.3.2 GUI library

AqDrv4.ini to indicate where FPGA .bit files can be found

- **Firmware** directory containing FPGA .bit files

- **lib** directory:

modules/acqrsPCI.o the device driver for Kernel 2.4.18 or RH8

modules/acqrsPCI.o.2.4.18-14

modules/acqrsPCI.o.2.4.20-8

alternate driver for Kernel 2.4.20 or RH9

**modules/acqrsPCI.ko.2.6.9-1.667** alternate driver for Kernel 2.6.9 or Fedora Core 3

modules/acqrsPCI.ko.2.6.9-1.667smp for above with SMP

■ modules/acqrsPCI.o.2.4.21-4.EL Red Hat Enterprise Linux version 3

modules/acqrsPCI.o.2.4.21-4.ELsmp for above with SMP

■ modules/acqrsPCI.ko.2.6.8-2-686 Debian Sarge

- **linuxdriverpci** directory:

Makefile to create acgrsPCI.o

LinuxGeneral.h header fileDDrIORules.h header file

• LinuxDriverPCI.c kernel driver main source code

• LinuxDriverPCI.h kernel driver header file

LinuxConfigPCI.c kernel driver configuration code

**Linux2.6driverpci** directory:

Makefile to create acqrsPCI.o

LinuxGeneral.h header fileDDrIORules.h header file

LinuxDriverPCI.c kernel driver main source code

# acgiris

• LinuxDriverPCI.h kernel driver header file

• LinuxConfigPCI.c kernel driver configuration code

- **usr/include** directory:

■ **AcqirisD1Import.h** Header file for C/C++

AcqirisD1Interface.h

Acqiris Device Driver Interface Definitions (API)

AcqirisDataTypes.h

Data Structure Header file for C/C++

AcqirisErrorCodes.h

Acqiris Error Code definitions

visatype.hVISA types

vpptype.h

usr/lib directory:

• libAnDBSLib.a Linux Acqiris library (compiled with gcc-3.2)

libAqLib.a Linux Acqiris base library

usr/src directory:

GetStarted Linux sample programGetStartedc Linux sample program

GetStarted.c Linux sample program source

GetStarted.cpp Linux sample program source

GetStarted.o Linux sample program object

Makefile makefile to create the application

# 3. Product Description

#### 3.1. Overview

Acqiris Analyzers are designed to provide superior measurement precision and accuracy. Key acquisition specifications (such as DC accuracy, integral and differential non-linearity) have been optimized to deliver maximum measurement fidelity. Careful circuit layout, custom IC's and special packaging techniques have all been employed to reduce the overall random and correlated system noise. The use of custom IC's also dramatically reduces the total number of discrete components required. This has tremendous benefits on reliability and also allows the modules to use a minimal amount of power.

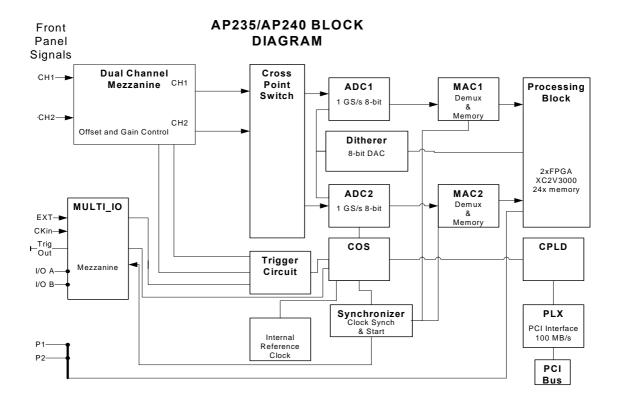

The AP series Analyzers are PCI modules that plug directly into any vacant PCI slot in a PC. They are fully programmable over the PCI bus and deliver 2 GS/s (AP240/AP201) and 1 GS/s (AP235/AP101) buffered acquisition performance. An acquired data sequence can be processed and transferred to a host processor over the PCI bus at speeds up to 100 Mbytes/s, *while simultaneously acquiring the next data sequence*.

For complete technical specifications concerning your particular analyzer please refer to the product's Specifications & Characteristics. In addition, Acqiris maintains up-to-date versions of all product data sheets on our web site (www.acqiris.com). The data sheets are available in pdf format and are best viewed using Adobe Acrobat software. If you have trouble accessing our web site, or viewing the data sheets, please contact your nearest sales office.

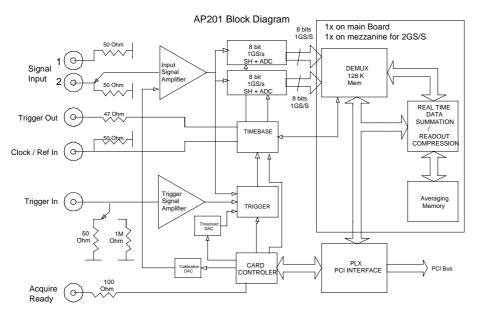

# AP201 Block Diagram

#### **Key features**

- **High Speed and Precision** The Acqiris Analyzers provide both high-speed acquisition capability and exceptionally high **simultaneous** data transfer rates to the host processor. The AP240 delivers real-time sampling rates of up to 2 GS/s with 1 GHz of analog bandwidth, while the AP201 delivers the same real-time sampling rates with 500 MHz of analog bandwidth, and the AP235 and AP101 offer sampling to 1 GS/s with 500 MHz of analog bandwidth.

- Signal conditioning The AP235/AP240 models include all the required input signal conditioning such as gain, from 50 mV to 5 V Full Scale, offset adjustment, bandwidth limiter, and 50 Ω DC coupling. The models AP101/AP201 Analyzer offer similar functionality with gains ranging from 50 mV to 500 mV Full Scale. The inputs are fully protected, and calibration is a built-in feature. A crystal controlled time base and advanced trigger circuits are used to allow fast and stable acquisitions.

- **Buffered Operation** All of the Acqiris Analyzers offer a buffered acquisition mode. A sequence of waveforms can be acquired while simultaneously processing and reading out a previously acquired waveform sequence. Data reduction through selective readout of pre-defined *gates* in each waveform segment is also possible. Furthermore the AP235/AP240 models implement a threshold gate readout mode that allows data driven readout of interesting data only. AP235/AP240 models with the AdvancedTDC option and the AP101/AP201 models support data processing to find peaks in the gates.

- Front panel control signals In order to ease the integration and synchronization of the Analyzer in a large variety of systems, a number of input and output signals are made available on the instruments front panel. Two MMCX connectors are dedicated to the Trigger Output and the Clock/Reference input, while two other MMCX connectors can be programmed for a variety of different usages, such as Trigger Ready, 10 MHz Reference Out or Sequence Stop. The AP235/AP240 offer the possibility of hardware reset of the segment timestamps through the P1 or P2 MMCX connectors.

- High Data Throughput All of the Acqiris Analyzers can easily be integrated into any standard computer with 1 free long PCI slot that provides the 3.3 V supply and adequate power required by the cards. Acquired data can be transferred, in DMA mode, directly to the processor over the PCI bus at rates of up to 100 Mbytes per second (4 ms for a 100 kpoints record, 10 ms for a 250 kpoints record, including DMA set up time overhead).

#### 3.2. Channel Input

The principle characteristics of the input channels are given in the table below:

| Model           | Bandwidth into 50 Ω    | Minimum<br>Rise Time | BW Limiter selections | Maximum<br>Full Scale | Maximum<br>Offset | Other particularities              |

|-----------------|------------------------|----------------------|-----------------------|-----------------------|-------------------|------------------------------------|

| AP240           | 1 GHz                  | 0.35 ns              | 20, 200, 700 MHz      | 5 V                   | 5 V               | 2 channels                         |

| AP235           | 0.5 GHz                | 0.7 ns               | 20, 200 MHz           | 5 V                   | 5 V               | 2 channels                         |

| AP101/<br>AP201 | 0.5 GHz for > 50 mV FS | 0.7 ns               | 25 MHz                | 0.5 V                 | 2 V               | 1 channel with 2 selectable inputs |

|                 | 200 MHz @<br>50 mV FS  | 1.8 ns               |                       |                       |                   |                                    |

## 3.2.1. Coupling & Impedance

Two 50  $\Omega$  signal input BNC connectors are provided. The AP240 and AP235 are two channel modules. In the case of the AP101 and AP201 these two connectors are multiplexed to the module's input. The active input may be selected by software to allow connection of one of the two possible signal sources. The 50  $\Omega$  coupling offers high quality termination with better than  $\pm$  1% precision. It is ideally suited for use with 50  $\Omega$  transmission lines.

All modules offer DC coupling. The AP240 and AP235 also provide AC coupling with a 32 Hz cutoff frequency.

## 3.2.2. Input Protection

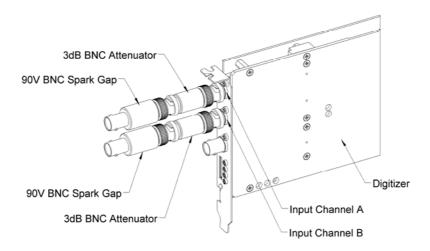

The input amplifiers are fully protected against over-voltage signals. The device can tolerate an input current of up to 40A for 1 µs without damage to the front-end electronics. For extreme cases, such as detector sparking, an external coaxial spark gap and attenuator can be supplied on request (See **Appendix A: XA100 BNC Input Overvoltage Protection**).

#### 3.2.3. Mezzanine Front-end

The front-end electronics are all mounted on a removable mezzanine card. In the event of accidental damage, or as components fatigue over time (e.g. relays in high duty cycle automated testing applications), the mezzanine card allows for fast and efficient replacement.

#### 3.2.4. Bandwidth and Rise Time

The bandwidth specification indicates the frequency at which an input signal will be attenuated by 3 dB (approximately 30% loss of amplitude). The bandwidth also affects the minimum rise and fall times that can be passed through the front-end electronics. A pulse with a very sharp edge will be observed to have a minimum rise time ( $\tau_{min}$ ) determined by the front-end electronics. In general a pulse with a given 10-90% rise time ( $\tau_{10-90real}$ ) will be observed with a slower value given by:

$$\tau_{\text{10-90}}^2 = \tau_{\text{10-90real}}^2 + \tau_{\text{min}}^2 \qquad \qquad \text{where} \quad \tau_{\text{min}}(\text{ns}) \approx 0.35 \text{ (GHz-ns)} \, / \, \text{BW (GHz)}$$

If desired, hardware bandwidth limiters can be selected.

## 3.2.5. Input Voltage and Offset

The input channel provides a fully programmable amplifier with variable input voltage and offset. Full Scale (FS) input voltages are selectable from 50 mV to the maximum indicated in the table above in a 1, 2, 5 sequence. Care should be taken to select an input voltage range that will allow the signal to be recorded using as much dynamic range of the digitizer as possible. Signals going outside of the FS Range will be clipped and data values for the clipped portion of a signal should be regarded as erroneous. The Variable Offset is programmable in the range of  $\pm 2$  V when using an FS Input Voltage setting of 500 mV or below, increasing to  $\pm 5$  V for FS settings above 500 mV. The raw 8 bit ADC data values are in the

range [-128,+127] with the first and last values reserved for underflow and overflow respectively. The midpoint value, 0, of the range corresponds to the negative of the offset voltage. Thus the Full Scale Range (FSR) goes from

Signals going outside of the FSR will be clipped and data values for the clipped portion of a signal should be regarded as erroneous.

#### 3.2.6. Vertical Resolution

The AP Series Analyzers use an ADC system with 8 bits of vertical resolution (256 levels). The dynamic range of the ADC covers the Full Scale (FS) of the Input Voltage setting. For example, if the Input Voltage is set to 500 mV then the ADC resolution is equivalent to 1.95 mV. To obtain the best dynamic range from the ADC care should be taken to ensure that the input signal varies over more than 50% of the Input Voltage Full Scale (FS) setting. The highest and lowest levels of the ADC correspond to underflow and overflow conditions.

# 3.2.7. DC Accuracy

The AP Series Analyzers use low noise front-end electronics in order to ensure voltage measurement is made with accuracy and precision. DC voltage accuracy is better than  $\pm$  2% ( $\pm$  1% typical) of the input voltage full-scale. The differential linearity is better than  $\pm$ 0.9 LSB for the AP235/AP240 and  $\pm$ 0.7 LSB for the AP101/AP201.

#### 3.3. Trigger

## 3.3.1. Trigger Source

The trigger source can be a signal applied to either of the Input Channels (for internal triggering) or the External Trigger Input.

The modules provide a front panel BNC External Trigger Input. The External Input provides a fully functional trigger circuit with selectable coupling, level and slope. The AP240 and AP235 have 50  $\Omega$  termination impedance with diode protection against overload. A  $\pm 5$  V limit on trigger signals should be respected, although somewhat higher voltages for short time periods will not damage the unit.

The AP101 and AP201 have both 1 M $\Omega$  and 50  $\Omega$  termination impedance. Overload protection will automatically switch the coupling from 50  $\Omega$  to 1 M $\Omega$  if the signal is greater than  $\pm 5$  V DC. If 50  $\Omega$  termination is selected a  $\pm 5$  V limit on trigger signals should be respected, although somewhat higher voltages for short time periods will not damage the unit. For 1 M $\Omega$  input, signals up to  $\pm 100$  V (DC + peak AC < 10 KHz) are allowed.

#### 3.3.2. Trigger Coupling

Trigger coupling is used to select the coupling mode applied to the input of the trigger circuitry. The AC LF Reject mode couples signals capacitively and removes the input signal's DC component and frequencies below 50 Hz for the AP240 and AP235 models (and 50 KHz for the AP101 and AP201). DC mode allows all signal components to be passed through to the trigger circuit. The AP240 and AP235 models have an HF Reject mode that removes signal components above 50 KHz. They also implement an HF trigger that allows triggers to be reliably accepted at rates above  $\sim 1$  GHz. In this mode, triggers occur on every fourth positive edge. In the HF mode negative slope and window triggers are not available.

## 3.3.3. Trigger Level

The trigger level specifies the voltage at which the selected trigger source will produce a valid trigger. The trigger level is defined as a set voltage. Using the internal trigger with DC coupling, the level is set with respect to the midpoint voltage ( $V_m$ = – Offset voltage) of the digitizer's vertical scale. All trigger circuits have sensitivity levels that must be exceeded in order for reliable triggering to occur.

The AP240 and AP235 offer level control for all trigger coupling modes. Internal trigger level settings (expressed in %) must be within  $V_m \pm 0.5$  FS, where FS is the channel Full Scale. In addition, they

implement a Window trigger. Two trigger level thresholds are used to define the desired range. The trigger can then be chosen to occur either when the signal exits or enters the window range. This mode can be thought of as the appropriate OR of two edge triggers of opposite slope.

For the AP101 and AP201 the AC coupled mode is implemented with an auto-level trigger. Internal trigger level settings for DC coupling must be within  $V_m \pm 0.6$  FS, where FS is the channel Full Scale.

The AP240 and AP235 models allow the user to choose the external trigger Full Scale from the set of values 0.5, 1.0, 2.0 or 5.0 V. The external trigger level can then be set to values in the range  $\pm$  0.5 FS. The AP101 and AP201 models have an external trigger range of  $\pm$  3 V.

The AP series Analyzers will trigger on signals with a peak-peak amplitude > 15% FS from DC to their bandwidth limit.

## 3.3.4. Trigger Slope

The trigger slope defines the direction of the signal that will be used to initiate the acquisition when it passes through the specified trigger level. Positive slope indicates that the signal is transitioning from a lower voltage to a higher voltage. Negative slope indicates the signal is transitioning from a higher voltage to a lower voltage.

## 3.3.5. External Trigger Output

When the module is ready to be triggered and a valid trigger signal occurs, a trigger output is generated for external use. It is always available on the Front Panel Trigger Out MMCX connector.

**NOTE:** The External Trigger Output functionality is implemented in the hardware. No Trigger Out signal occurs for software-generated triggers such as those of the AUTO mode of APx01Demo or through the use of the function **AcqrsD1\_forceTrigger**.

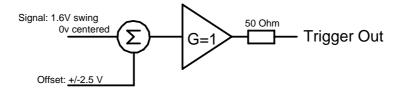

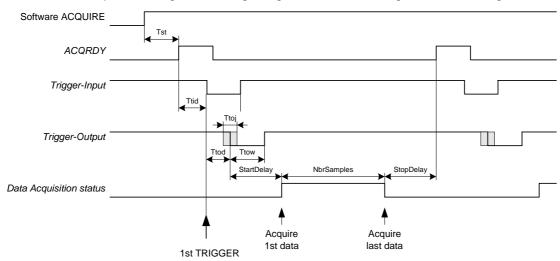

Trigger Output Block diagram:

The output swing is 1.6 V ( $\pm$  0.8 V) when unloaded and 0.8 V when terminated on 50  $\Omega$ . The rise and fall times are 2.5 ns typical. The offset can be adjusted, by software control in the range [-2.5 V, +2.5 V] unloaded, or [-1.25 V, +1.25 V] into 50  $\Omega$ . The maximum output current capability is  $\pm$  15 mA. As the output is retro-terminated, it is possible to drive a 50  $\Omega$  line unterminated (HiZ) without loss of performance.

For a TTL compatible signal, set the offset to 1.0 V and the swing at destination will be +0.2 to +1.8 V.

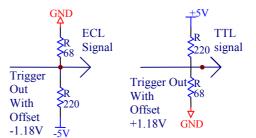

For an ECL compatible signal, terminated on 50  $\Omega$  to -1.2 V, set the offset to -1.2 V and the output will be in the range [-0.8 V, -1.6 V]).

Alternatively, to reduce the current drawn from the digitizer, the terminations below can be used:

#### 3.3.6. Trigger Status

The front panel includes a tri-color LED indicator to show the status of the trigger. When the LED is green it indicates the trigger is armed and waiting for a valid trigger to occur. Red indicates that the trigger has occurred, the acquisition is complete and the data is waiting to be readout. The user can override the default functions and program the LED color in an application-specific manner.

#### 3.3.7. Trigger Veto and Timeout (AP101/AP201 ONLY)

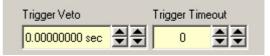

Certain applications can generate a *Prepare for Trigger* signal that can be generated just before a window in time for an acceptable trigger. An Analyzer in the buffered data acquisition mode (see **AcqrsD1\_configMode**) can be configured to recognize the *Prepare for Trigger* signal on the MMCX IO A or B connector (see **AcqrsD1\_configControlIO**) and wait a software selectable time before accepting a trigger. This veto time can be set in the range [0 s, 1 s] in steps of 30 ns. The Trigger Veto feature is useful in applications where an early echo (response signal) should be ignored.

Furthermore, if desired, the Analyzer can be asked to generate an artificial trigger if no real trigger occurs after the window has been open for a time that can also be set in that same range. This is a way to ensure that there will be data associated with every *Prepare for Trigger* signal even if no real trigger occurs. A *Prepare for Trigger* Signal can only be accepted after the ACQRDY has been generated. The data values for an artificial trigger will all be -128 = 0x80 and the time taken to generate this special acquisition will be the same as for a real trigger. The Timeout feature is useful to ensure the correct pairing of stimulus and response and to avoid unwanted "hung" states where the Analyzer is waiting for a trigger that will never occur.

#### 3.4. Data Acquisition – Common

The AP series Analyzers can be used either for buffered acquisition with analysis or normal digitizer data acquisition. These two modes are quite different in their functioning. After describing some common characteristics they will be treated individually in the sections below. The digitizer mode is particularly useful when trying to configure an AP module for later use as an analyzer.

## **3.4.1.** Timing

A crystal controlled time base is used to generate the clock of the digitizer. Clock accuracy is better than  $\pm$  2 ppm, and individual sample points are recorded with better than  $\pm$  10 ps (< 2 ps rms) of sampling jitter.

## 3.4.2. Sampling Rate

The AP series Analyzers include an analog-to-digital converter (ADC) that can sample waveforms in real time, at rates from 1 or 2 GS/s (0.5 ns per point) down to 100 S/s (10 ms per point). The sampling rate can be programmed and is selectable in a 1, 2, 2.5, 4, 5 sequence (i.e. 100 MS/s, 200 MS/s, 250 MS/s, 400 MS/s, 500 MS/s, 1GS/s, 2GS/s).

## 3.5. Data Acquisition - Digitizer Mode

#### 3.5.1. Acquisition Memory and Time Base Range - Digitizer Mode

Data from the ADC are stored in on-board acquisition memory. The amount of memory in use for acquisition can be programmed and is selectable from 2 points to 261350 points, the full amount of acquisition memory available. Note that the analyzer mode memory is much greater.

For technical reasons, a certain memory "overhead" is required for each waveform, reducing the available memory by a small amount. In order to simplify programming, Acqiris provides an interface function, which recommends the best sampling rate and the maximum possible number of data points, taking into account the available memory, the requested time window, the number of segments (in Sequence mode), as well as the required memory overhead.

The Time Base Range defines the time period over which data is being acquired. For example, the AP201 in the digitizer mode has an acquisition memory of just under 256 Kpoints and maximum sampling rate of 2 GS/s. Thus, at the maximum sampling rate, the digitizer can record a signal over a time period of up to 130 µs (256 Kpoints \* 0.5 ns/point). The time base range can be adjusted by varying the amount of acquisition memory or the sampling rate of the digitizer.

#### 3.5.2. Pre- and Post-Trigger Delay - Digitizer Mode

To increase trigger flexibility a pre- or post-trigger delay can be applied to the trigger position. However, pre-trigger is not available in the analyzer mode.

The amount of pre-trigger delay can be adjusted between 0 and 100% of the acquisition time window (i.e. sampling interval x number of samples), whereas the post-trigger delay can be adjusted between 0 and 200 million samples.

Pre- or post-trigger delays are just different aspects of the same trigger positioning parameter:

- The condition of 100% pre-trigger indicates that all data points are acquired prior to the trigger, i.e. the trigger point is at the **end** of the acquired waveform.

- The condition of 0% pre-trigger (which is identical to a post-trigger of 0) indicates that all data points are acquired immediately after the trigger, i.e. the trigger point is at the **beginning** of the acquired waveform.

- The condition of a non-zero post-trigger delay indicates that the data points are acquired after the

trigger occurs, at a time that corresponds to the post-trigger delay, i.e. the trigger point is before the

acquired waveform.

The digitizer hardware accepts pre- and post-trigger adjustments in increments of 16 samples. By definition post-trigger settings are a positive number and pre-trigger settings are a negative number.

Thus it is only natural that the software drivers provided by Acqiris treat pre- and post-trigger delays as a single parameter in seconds that can vary between —nbrSamples \* samplingInterval (100% pre-trigger) and +maxPostTrigSamples \* samplingInterval (max post-trigger). Since the Acqiris software drivers provide very accurate trigger position information upon waveform readout, the accepted resolution of the user-requested pre-/post-trigger delay is much better than 16 samples. For more details, refer to the **Programmer's Reference Manual.**

#### 3.5.3. Single and Sequence Acquisitions - Digitizer Mode

Digitizers acquire waveforms in association with triggers. Each waveform is made of a series of measured voltage values (sample points) that are made by the ADC at a uniform clock rate. To maximize sampling rates and utilize memory as efficiently as possible, the digitizers include both Single and Sequential storage modes.

The Single Acquisition mode is the normal operation of most digitizer products. In this mode an acquisition consists of a waveform recorded with a single trigger. The user selects the sampling rate and acquisition memory size and sets the number of segments to 1 (default value).

The modules also include a built-in Trigger Time Interpolator (TTI) that measures the time from the trigger point to the first sample point. This information is essential for determining the precise relation between the trigger or other event of interest and the digitized samples of the signal. The TTI resolution is 80 ps.

The Sequence Acquisition mode allows the capture and storage of consecutive "single" waveforms. Sequence Acquisition mode is useful as it can optimize the digitizer's sampling rate and memory requirements for applications where only portions of the signal being analyzed are important. The mode is extremely useful in almost all impulse-response type applications (RADAR, SONAR, LIDAR, Time-of-Flight, Ultrasonics, Medical and Biomedical Research, etc.).

In Sequence Acquisition mode the acquisition memory is divided into a pre-selected number of segments. Waveforms are stored in successive memory segments as they arrive. Each waveform requires its own individual trigger. The memory can be divided into any number of segments between 2 and 200. In Sequence Acquisition mode the user needs to specify the sampling rate, the total acquisition memory and number of segments. Note that the Single Acquisition mode is just a special case of the Sequence Acquisition mode with the number of segments set to 1.