# **STR340**

# Struck Fastbus Interface April 1996

<u>Titel</u>: Struck Fastbus Interface

Projekt : STR340/SFI

Autor : Tino Haeupke (email: th@struck.de)

Version : 1.0

Erstellungsdatum : letzte Änderung : 1.8.95

15.07.96 14:45

Filename : S340\_MAN.DOC

# **CONTENS**

| 1 GENERAL INFORMATION                                                                                                                                              | 5                     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| 1.1 Purpose                                                                                                                                                        | 5                     |

| 1.2 Product Assistance                                                                                                                                             | 5                     |

| 1.3 Note                                                                                                                                                           | 5                     |

| 2 SFI INTRODUCTION                                                                                                                                                 | 6                     |

| 2.1 FASTBUS transactions                                                                                                                                           | 8                     |

| 2.2 Auxiliary Connector                                                                                                                                            | 8                     |

| 2.3 Future extension                                                                                                                                               | 9                     |

| 2.4 FASTBUS Master Port                                                                                                                                            | 10                    |

| 3 SFI VME SLAVE ADDRESS MAP                                                                                                                                        | 12                    |

| 4 SFI VME SLAVE REGISTER                                                                                                                                           | 13                    |

| 4.1 Sequencer Status register (R)                                                                                                                                  | 13                    |

| 4.2 FASTBUS Status register 1 (R)                                                                                                                                  | 14                    |

| 4.3 FASTBUS Status register 2 (R)                                                                                                                                  | 15                    |

| 4.4 FASTBUS Last Primary Address Store register (R)                                                                                                                | 15                    |

| 4.5 Last Sequencer Protocol (Sequencer Keyaddress) register (R)                                                                                                    | 16                    |

| 4.6 Next Sequencer Ram Address register (R/W)                                                                                                                      | 17                    |

| 4.7 FASTBUS Timeout register (R/W)                                                                                                                                 | 18                    |

| 4.8 FASTBUS Arbitration Level register (R/W)                                                                                                                       | 18                    |

| 4.9 FASTBUS Protocol signal register (R)                                                                                                                           | 19                    |

| 4.10 Sequencer Fifo Flag and ECL/NIM Input register (R)                                                                                                            | 20                    |

| <ul><li>4.11 Out-Signal register (W)</li><li>4.11.1 VME Out-Signal register</li><li>4.11.2 Sequencer Out-Signal register (writeable from the sequencer!)</li></ul> | <b>21</b><br>21<br>22 |

| 4.12 VME IRQ Source and MASK register                                                                                                                              | 23                    |

| 4.13 VME IRQ Level and Vector register                                                                                                                             | 24                    |

| 5 VME INTERRUPTS                                                                                                                                                   | 25                    |

|                                                                                                                                                                    |                       |

| 6 FASTBUS MASTER SEQUENCER                                                                                                                                                                                                                                                                                                                                                           | 26                                           |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| 6.1 Sequencer Enable (arm)                                                                                                                                                                                                                                                                                                                                                           | 26                                           |

| <ul> <li>6.2 Sequencer FiFo Key Addresses</li> <li>6.2.1 FASTBUS actions</li> <li>6.2.1.1 Mode register and Limit counter (Sequencer Load)</li> <li>6.2.1.2 DMA Status register and Word Counter (Sequencer Store)</li> <li>6.2.1.3 FASTBUS command key address assignments</li> <li>6.2.1.4 FASTBUS cycle command list examples</li> <li>6.2.2 Sequencer Control actions</li> </ul> | 27<br>27<br>28<br>28<br>29<br>30<br>31       |

| 6.3 Sequencer RAM 6.3.1 Sequencer RAM Loading 6.3.2 Sequencer RAM List execution                                                                                                                                                                                                                                                                                                     | <b>32</b><br>32<br>32                        |

| 6.4 Sequencer Programming Examples 6.4.1 FASTBUS initialization routine 6.4.2 Single FWC routine 6.4.3 Single FRD routine 6.4.4 Single FRDB routine 6.4.5 Load Next EVENT and FRDB List execution example 6.4.6 Load a Command List in the Sequencer Ram example 6.4.7 Event Readout example using a Ram List                                                                        | 33<br>33<br>33<br>34<br>35<br>36<br>37<br>38 |

| 7 AUXILIARY CONNECTOR INTERFACE                                                                                                                                                                                                                                                                                                                                                      | 40                                           |

| 7.1 Auxiliary Connector schematic                                                                                                                                                                                                                                                                                                                                                    | 40                                           |

| 7.2 User Trigger interface                                                                                                                                                                                                                                                                                                                                                           | 41                                           |

| 7.3 FASTBUS blocktransfer Direct Mode interface                                                                                                                                                                                                                                                                                                                                      | 43                                           |

| 8 FRONT PANEL                                                                                                                                                                                                                                                                                                                                                                        | 44                                           |

| 8.1 LEDs                                                                                                                                                                                                                                                                                                                                                                             | 44                                           |

| 8.2 Inputs/Outputs 8.2.1 Schematic differential ECL In/Output 8.2.2 Schematic NIM In/Output                                                                                                                                                                                                                                                                                          | <b>45</b><br>46<br>47                        |

| 9 POWER REQUIREMENTS FOR THE SFI                                                                                                                                                                                                                                                                                                                                                     | 48                                           |

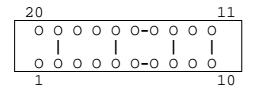

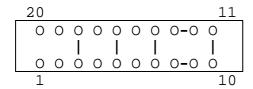

| 10 JUMPER                                                                                                                                                                                                                                                                                                                                                                            | 49                                           |

## 1 GENERAL INFORMATION

#### 1.1 Purpose

The **SFI** (**S**TRUCK **F**ASTBUS **I**nterface) is a FASTBUS Master based on a standard VMEbus CPU. That allows the user to choose a wellknown CPU and operating system and to drive FASTBUS with that.

#### 1.2 PRODUCT ASSISTANCE

We afford assistance to SFI users to allow for a short implementation time for user specifier application by the following means:

- \* Example code for OS9 (K&R style C) is supplied with SFI

- \* Address questions relating SFI hard- and software to SFI@struck.de

- \* Send an email containing your SFI's serial number and the used VMEbus CPU and operating system to SFI@struck.de . We would like to use your email address for information exchange with other users (only with your permission).

## **1.3 Note**

\* The cover sheet is hard anodized so that the surface is insulating. Additional, the inside VME area has been provided with a plastic foil in addition. Please, slide in (or out) carefully the left VME module to protect the foil.

## \* VME BUS Daisy chain

If no VMEbus module is installed in the second VMEbus Slot (right VMEbus slot side) of the SFI2, so you have to place a "dummy" Daisy Chain VMEBus connector on the P1 connector (upper one).

#### \* Auxiliary Connector

The Auxiliary connector is **used** on the SFI. Make sure that no incompatible auxiliary board is plugged in.

## **2 SFI INTRODUCTION**

The SFI is a powerful and simple Fastbus Master and Readout Controller **using commercial off-the-shelf 6U VME CPU** (or Master) module as local intelligence. Using already established real time operating systems on these modules (like OS-9, VxWorks, LynxOS or even MS-Windows Derivates), programming of FASTBUS applications is simplified and allow direct code portation.

One or two (more on request) 6U VME modules can be plugged into the SFI FASTBUS module. For example, you can operate a powerful VME configuration consisting of a CPU (68040, R3000, Power-PC or DSP based) together with a communication interface module (like Fibre channel, ATM, VICbus etc.) locally and directly in a FASTBUS crate.

Another possibility is to operate a single VME processor with an on-board communication interface based for instance upon PCI local bus mezzanines (available from vendors are PCI-ATM, PCI-Fibre channel, PCI-SCI etc.).

The interface between the VME-CPU and the FASTBUS Segment guarantees highest possible performance in speed, flexibility and reliability.

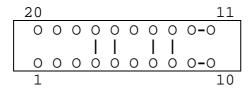

file: s340\_blk.vsd

Blockdiagram: SFI

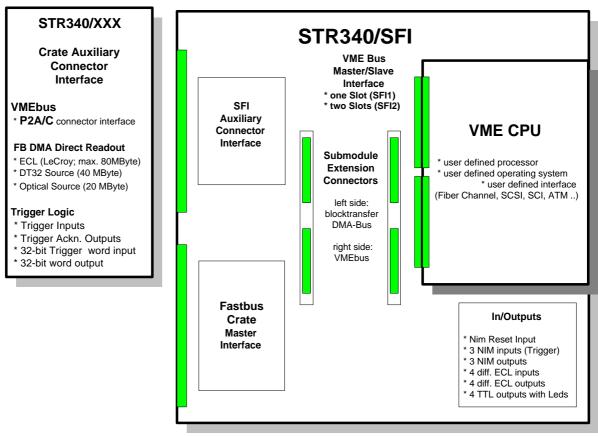

Blockdiagram: Data Flow

#### 2.1 FASTBUS TRANSACTIONS

FASTBUS transactions are executed by a high speed hardware sequencer logic. Using a simple programming model FASTBUS transactions are defined by a list of VME key address cycles. In order to gain in speed VME key address lists and data are passed through a FIFO to the sequencer. Applying this technique FASTBUS cycles and instructions can be executed already during the write list phase in an overlap mode. Synchronisation of list execution with external NIM/ECL signals is implemented too.

**FASTBUS** blocktransfer read sequences are transformed into VME blocktransfer sequences or single cycles (if the **VME mode** is enabled). In this case, the SFI on-board DMA controller passes the FASTBUS data through a derandomizing FASTBUS-data FIFO directly into the VME-CPU memory (partitioned in multiple 256 byte blocks in the case of large blocks). **In this case, the SFI controller acts as the (internal) "VME Master".**

Another important feature is the **direct mode** via the FASTBUS Auxiliary connector. In this mode, the FASTBUS data, reading in blocktransfer mode, are pushed through Buffer/Latches to the FASTBUS Auxiliary connector controlled via several protocol lines. A simple logic on an auxiliary module converts the FASTBUS data into strobed differential ECL outputs (LeCroy ECLine compatible), into serial optical data stream (STR333/S) or into a private data stream format. Protocol compatibility to LeCroy ECLine offers to pass the data stream into buffer memories and/or DSP based Input FiFos (e.g. Struck VME STR8090 or FASTBUS STR370 DSP96002 Systems).

The VME mode and the direct mode can also enabled at the same time. In this case data are pushed into the VME slave memory (CPU or other VME module) <u>and</u> to the Auxiliary connector interface (SPY Mode).

A complete FASTBUS crate scan and readout sequence consisting of an arbitrary mixture of FASTBUS transactions (typically address locks, secondary address writes, multi block reads, single block reads, local broadcasts etc.) is executed by the list sequencer in one "stream".

#### 2.2 AUXILIARY CONNECTOR

The Auxiliary connector provides the following features:

- \* connection to the VME P2 A/C connector from the leftside VME modul

- \* FASTBUS blocktransfer DIRECT Mode

- \* user Trigger interface (write/read 32-bit word, receive signals, assert signals)

## 2.3 FUTURE EXTENSION

In order to offer even higher flexibility and speed, VMEbus and FASTBUS DMA Bus submodule extension SMD connectors are implemented. These SMD connectors allow to add different kind of user defined logic.

For example a local memory buffer with up to 128Mbyte of fast dual ported DRAM, which is able to accept FASTBUS data streams at a sustained rate of 40Mbyte/s. Using this buffer it is possible to cover up to three seconds of data taking at highest FB speed for instance during a accelerator beam spill. Emptying of the buffer, for instance during a spill pause, can be performed by the VME CPU with D64 blocktransfer read cycles, passing the data into communication channels like Fibre Channel, ATM etc., or for example a memory look-up table to filter and convert the data, eg..

Blockdiagram: example of a look-up table to filter and convert data

## 2.4 FASTBUS MASTER PORT

Due to the special attributes and complexity of FASTBUS operations, especially compound cycles like <address lock, secondary address write, data read, address release> and also complex status responses on SS-lines, the SFI does not use a direct, synchronous transformation method between VME action(s) and FASTBUS action(s). In this case route/mapping look up tables and SS-response handling methods would cause many complications.

Instead, the SFI implements a transformation method between VME and FASTBUS actions using so called **Key Address Technique**.

Key Address Technique means that certain VME address keys are used to execute ("to open") certain types of FASTBUS transactions. The actual transaction is defined in detail by accompanying data (for instance the key address operation to establish an address lock has to be accompanied by the geographical or logical address in the data part of the VME cycle.) VME Key address cycles are even used to program and define the SFI DMA controller (Setting word/limit counter, address pointer). A set of successive key address cycles forms a **list of SFI/FASTBUS transactions**, which is interpreted and executed by the sequencer logic.

In order to increase the FASTBUS system performance the VME key address cycles and the FASTBUS list interpreter are not directly coupled (or synchronized). Instead, the key address information together with its data information are written into a decoupling FIFO (or RAM, see below) at highest VME speed. As soon as the first words have rippled through the FIFO, the list sequencer starts the corresponding FASTBUS or internal actions in an overlapping mode.

Another advantage of this technique is, that error conditions (Time out, or SS-response >0) are not handled by special CPU Bus Errors or Traps, instead the FASTBUS Master sequencer handles the exceptions (also SI support) and informs the VME CPU by polling a register or an VME Interrupt. FASTBUS and Sequencer status registers can be read to achieve the required status information.

Data, which are read from FASTBUS in single cycle mode (not with the autonomous blocktransfer), are passed directly into the sequencer Data Output FIFO (SEQ2VME Fifo).

With the sequencer FIFO key addresses it is also possible to execute the following special functions:

- start autonomous blocktransfer (High speed FB blocktransfer, DK(t) to DS(t) =35ns to 45 ns)

- load DMA limitcounter (=max. blocklength)

- load DMA address pointer (VME Slave address; A32)

- store DMA wordcounter, Timeout information and SS-response in the Data Output Fifo (SEQ2VME Fifo)

- store only DMA wordcounter

- generate VME interrupt

- set/clear external signals (NIM, ECL)

- set/clear Leds

#### **Sequencer RAM**

In parallel to the FIFO a Sequencer List RAM is implemented in order to store a complete list and to start the execution of the entire list without rewriting the list elements into the FIFO. This feature allows for instance to initialize a compound FB crate readout sequence of multiple TDC's and ADC's with one single VME cycle.

**Blockdiagram:** FASTBUS Master Sequencer

# 3 SFI VME SLAVE ADDRESS MAP

The SFI VME Slave logic can be addressed with the VME Address Modifier AM=39 and AM=3D (A24/D32).

The VME Base Address (b) is to choose with the 4-bit switch SW850.

Factory setting: SW850 = E ==> \$E00000.

For processor data cache and Compiler optimizer problems it is helpful to use different addresses (different x) for read and write cycles!

| A24 address | R/W | function                                                |  |  |

|-------------|-----|---------------------------------------------------------|--|--|

| (A24/D32)   |     | (x = don't care)                                        |  |  |

| \$ b0 1x 00 | R   | Internal FASTBUS I/O Bus                                |  |  |

| \$ b0 1x 04 | R   | FASTBUS Last Primary Address Store register             |  |  |

| \$ b0 1x 00 | W   | Write VME Out-Signal register (LEDs, ECL, NIM, AUX )    |  |  |

| \$ b0 1x 04 | W   | Key Address: clear VME Out-Signal register              |  |  |

| \$ b0 1x 10 | W   | Write to internal AUX-port register                     |  |  |

| \$ b0 1x 14 | W   | Key Address: generate AUX_B40 pulse                     |  |  |

| \$ b0 2x 00 | R   | FASTBUS Timeout register                                |  |  |

| \$ b0 2x 04 | R   | FASTBUS Arbitration Level register                      |  |  |

| \$ b0 2x 08 | R   | FASTBUS Protocol Signal register                        |  |  |

| \$ b0 2x 0C | R   | Sequencer Fifo Flag and ECL/NIM Input register          |  |  |

| \$ b0 2x 10 | R   | VME IRQ Level and Vector register                       |  |  |

| \$ b0 2x 14 | R   | VME IRQ Source and Mask register                        |  |  |

| \$ b0 2x 18 | R   | Next Sequencer Ram Address register                     |  |  |

| \$ b0 2x 1C | R   | Last Sequencer Protocol (Sequencer Keyaddress) register |  |  |

| \$ b0 2x 20 | R   | Sequencer Status register                               |  |  |

| \$ b0 2x 24 | R   | FASTBUS Status register 1 (Arbitration/Primary Status)  |  |  |

| \$ b0 2x 28 | R   | FASTBUS Status register 2 (Data cycle/DMA Status)       |  |  |

| \$ b0 2x 00 | W   | FASTBUS Timeout register                                |  |  |

| \$ b0 2x 04 | W   | FASTBUS Arbitration Level register                      |  |  |

| \$ b0 2x 08 | W   | reserved                                                |  |  |

| \$ b0 2x 0C | W   | reserved                                                |  |  |

| \$ b0 2x 10 | W   | VME IRQ Level and Vector register                       |  |  |

| \$ b0 2x 14 | W   | VME IRQ Mask register                                   |  |  |

| \$ b0 2x 18 | W   | Next Sequencer RAM Address register                     |  |  |

| \$ b0 2x 1C | W   | Key Address : Reset register group LCA2 ( xx 20 xx)     |  |  |

| \$ b0 2x 20 | W   | Key Address: Sequencer Enable                           |  |  |

| \$ b0 2x 24 | W   | Key Address: Sequencer Disable                          |  |  |

| \$ b0 2x 28 | W   | Key Address: Sequencer Ram Load Enable                  |  |  |

| \$ b0 2x 2C | W   | Key Address: Sequencer Ram Load Disable                 |  |  |

| \$ b0 2x 30 | W   | Key Address: Sequencer Reset                            |  |  |

| \$ b0 2x 38 | W   | Key Address: Clear Sequencer CMD Flag                   |  |  |

| \$ b0 4x xx | R   | Read SEQ2VME Fifo                                       |  |  |

| \$ b1 xx xx | W   | Write VME2SEQ Fifo                                      |  |  |

# 4 SFI VME SLAVE REGISTER

# 4.1 SEQUENCER STATUS REGISTER (R)

This register is a read only register for the Sequencer Status information.

| bit | name           | function                                                                 |  |

|-----|----------------|--------------------------------------------------------------------------|--|

| 31  | reserved       | "1"                                                                      |  |

|     |                |                                                                          |  |

| 16  | reserved       | "1"                                                                      |  |

|     |                |                                                                          |  |

| 15  | SEQ_DONE       | indicates that the Sequencer is in idle Loop or Sequencer is disabled    |  |

| 14  | SEQ_BUSY       | indicates that the Sequencer is BUSY (valid only if SEQ_ENABLE)          |  |

| 13  | SEQ_IDLE       | indicates that the Sequencer is IDLE (Enabled but no new Command)        |  |

| 12  | reserved       | "0"                                                                      |  |

|     |                |                                                                          |  |

| 11  | CMD_CTR        | indicates that the Sequencer works on a Control command                  |  |

| 10  | CMD_PRIM       | indicates that the Sequencer works on a Arbitration or Primary Address   |  |

|     |                | command                                                                  |  |

| 9   | CMD_DATA       | indicates that the Sequencer works on a FB Data Cycle                    |  |

| 8   | CMD_DMA        | indicates that the Sequencer works on a FB DMA Blocktransfer             |  |

|     |                |                                                                          |  |

| 7   | SEQ_DMA_ERROR  | indicates an error during FB DMA Blocktransfer Cycle                     |  |

| 6   | SEQ_DATA_ERROR | indicates an error during FB Data Cycle                                  |  |

| 5   | SEQ_PRIM_ERROR | indicates an error during Arbitration or Primary Address Cycle           |  |

| 4   | SEQ_CMD_ERROR  | indicates an invalid Sequencer Command (undefined Sequencer Key address) |  |

|     |                |                                                                          |  |

| 3   | SEQ_WAIT       | Sequencer waits for an external or internal event (reserved)             |  |

| 2   | SEQ_RAM_LOAD   | Sequencer is in the Sequencer RAM Load Mode                              |  |

| 1   | SEQ_RAM_ENABLE | Sequencer is enabled and in Sequencer Ram Mode                           |  |

| 0   | SEQ_ENABLE     | Sequencer is enabled (Fifo or RAM Mode)                                  |  |

Value after Power-up Reset, Reset or Key Address "Reset register group LCA2": 0xFFFF0000

# 4.2 FASTBUS STATUS REGISTER 1 (R)

This register is a read only register. In case of a Sequencer Primary Address cycle error (bit SEQ\_PRIM\_ERROR in the Sequencer Status register is set), this register gives more detailed information about the reason.

| bit | name             | function                                                                   |  |

|-----|------------------|----------------------------------------------------------------------------|--|

| 31  | reserved         | "1"                                                                        |  |

|     |                  |                                                                            |  |

| 16  | reserved         | "1"                                                                        |  |

|     |                  |                                                                            |  |

| 15  | reserved         | "1"                                                                        |  |

| 14  | reserved         | "1"                                                                        |  |

| 13  | reserved         | "1"                                                                        |  |

| 12  | reserved         | "1"                                                                        |  |

|     |                  |                                                                            |  |

| 11  | reserved         | "0"                                                                        |  |

| 10  | PRIM_AK_TIMEOUT2 | Primary Address Cycle (AK) Timeout and WT is actice                        |  |

|     |                  | > SI (Segment Interconnect) Farside Timeout                                |  |

| 9   | PRIM_AK_TIMEOUT1 | normal Primary Address cycle (AK) Timeout                                  |  |

| 8   | reserved         | "0"                                                                        |  |

|     |                  |                                                                            |  |

| 7   | PRIM_SS_STOP     | indicates that the last Primary Address cycle stops with SS-response < > 0 |  |

| 6   | PRIM_SS2         | SS2 bit of last Primary Address cycle                                      |  |

| 5   | PRIM_SS1         | SS1 bit of last Primary Address cycle                                      |  |

| 4   | PRIM_SS0         | SS0 bit of last Primary Address cycle                                      |  |

|     |                  |                                                                            |  |

| 3   | PRIM_ERROR3      | set AS Timeout; not possible to set AS (WT)                                |  |

| 2   | PRIM_ERROR2      | pending Master but other Master still active (Longtime Timeout)            |  |

| 1   | ARB_ERROR1       | Arbitration Timeout                                                        |  |

| 0   | PRIM_ERROR1      | try to set AS but already ASAK Lock is set                                 |  |

Value after Power-up Reset, Reset or Key Address "Reset register group LCA2": 0xFFFFF000

# 4.3 FASTBUS STATUS REGISTER 2 (R)

This register is a read only register. In case of a Sequencer Data or DMA(blocktransfer) cycle error (bit SEQ\_DATA\_ERROR or bit SEQ\_DMA\_ERROR in the Sequencer Status register is set), this register gives more detailed information about the reason.

| bit | name            | function                                                       |

|-----|-----------------|----------------------------------------------------------------|

| 31  | reserved        | "1"                                                            |

|     | reserved        |                                                                |

| 16  | reserved        | <br>"1"                                                        |

| 10  | reserved        |                                                                |

| 15  | DMA_DONE        | indicates that the DMA is finished                             |

| 14  | DMA_BUSY        | indicates that the DMA is BUSY                                 |

| 13  | DMA_VME_TIMEOUT | indicates a VME TIMEOUT during last DMA                        |

| 12  | DMA_FB_TIMEOUT  | indicates a FASTBUS Timeout during last DMA                    |

|     |                 |                                                                |

| 11  | DMA_LIMIT       | indicates that the last DMA stops by Limit Counter             |

| 10  | DMA_SS2         | shows the SS2 bit from last DMA                                |

| 9   | DMA_SS1         | shows the SS1 bit from last DMA                                |

| 8   | DMA_SS0         | shows the SS0 bit from last DMA                                |

|     |                 |                                                                |

| 7   | DATA_SS_STOP    | indicates that the last Data Cycle stops with SS-response <> 0 |

| 6   | DATA_SS2        | SS2 bit of last Data Cycle                                     |

| 5   | DATA_SS1        | SS1 bit of last Data Cycle                                     |

| 4   | DATA_SS0        | SS0 bit of last Data Cycle                                     |

|     |                 |                                                                |

| 3   | DATA_ERROR4     | DK Timeout                                                     |

| 2   | DATA_ERROR3     | set DS Timeout (not possible to set DS, WT)                    |

| 1   | DATA_ERROR2     | DK is set !!!                                                  |

| 0   | DATA_ERROR1     | no ASAK Lock                                                   |

Value after Power-up Reset, Reset or Key Address "Reset register group LCA2": 0xFFFF0000

# 4.4 FASTBUS LAST PRIMARY ADDRESS STORE REGISTER (R)

This register is a 32-bit read only register and it is updated with the Fastbus AD lines (primary address) by each Primary Address cycle of the SFI. This register is helpfull for error debuging by executing a FASTBUS command list to find out in an error case with which FASTBUS slave the error occured.

Value after Power-up Reset or Reset: 0x00000000

# 4.5 LAST SEQUENCER PROTOCOL (SEQUENCER KEYADDRESS) REGISTER (R)

This register is a read only register and it is updated with sequencer protocol command by each reading of the next sequencer protocol command from the VME2SEQ sequencer protocol Fifo. In case of a sequencer command error (bit SEQ\_CMD\_ERROR in the Sequencer Status register is set), this register stores the last protocol command.

| bit | nama      | function                           |

|-----|-----------|------------------------------------|

|     | name      | "1"                                |

| 31  | reserved  |                                    |

|     |           | ••                                 |

| 16  | reserved  | "1"                                |

|     |           |                                    |

| 15  | L_SEQ_A15 | last sequencer key address bit A15 |

| 14  | L_SEQ_A14 | last sequencer key address bit A14 |

| 13  | L_SEQ_A13 | last sequencer key address bit A13 |

| 12  | L_SEQ_A12 | last sequencer key address bit A12 |

|     |           |                                    |

| 11  | L_SEQ_A11 | last sequencer key address bit A11 |

| 10  | L_SEQ_A10 | last sequencer key address bit A10 |

| 9   | L_SEQ_A9  | last sequencer key address bit A9  |

| 8   | L_SEQ_A8  | last sequencer key address bit A8  |

|     |           |                                    |

| 7   | L_SEQ_A7  | last sequencer key address bit A7  |

| 6   | L_SEQ_A6  | last sequencer key address bit A6  |

| 5   | L_SEQ_A5  | last sequencer key address bit A5  |

| 4   | L_SEQ_A4  | last sequencer key address bit A4  |

|     |           |                                    |

| 3   | L_SEQ_A3  | last sequencer key address bit A3  |

| 2   | L_SEQ_A2  | last sequencer key address bit A2  |

| 1   | reserved  | "1"                                |

| 0   | reserved  | "1"                                |

Value after Power-up Reset or Reset: 0xFFFF0003

## 4.6 NEXT SEQUENCER RAM ADDRESS REGISTER (R/W)

This register stores the Sequencer Ram address pointer. It is used either for loading a command list or for executing a command list.

In case of loading a command list this register will be loaded with the ram address via the VME CPU. Then the CPU has to enable the ram load mode. Now the CPU can write the command list into the VME2SEQ Fifo. The sequencer ram load logic reads the Fifo (if not empty) and writes the reading data (protocol and data) into the sequencer ram and increments the address pointer automatically. After the CPU has written the full command list into the Fifo (indirect to the sequencer ram) it is possible to read the address pointer to check or to store the end address.

In case of executing a command list this register will be loaded with the start ram address via the sequencer. The sequencer can only load addresses on a 0x100 boundary (0x0, 0x100, 0x200, ....). The sequencer increments also the address pointer automatically. After executing the command list it is possible to read the address pointer via the CPU to check the end address or in an error case it is possible to find out on which command the error occurred.

It is **only possible** to load this register (write to this register) from the VME CPU with a new sequencer ram address pointer **if the sequencer is not enabled** and **if the sequencer is not in the sequencer ram load mode.**

It is **only allowed to read** the address pointer if the sequencer is **not in ram load mode** or if the sequencer is **not in the ram mode**.

| bit | name        | R/W        | function                                                            |

|-----|-------------|------------|---------------------------------------------------------------------|

| 31  | reserved    | read only  | "1"                                                                 |

|     |             |            |                                                                     |

| 16  | reserved    | read only  | "1"                                                                 |

|     |             |            |                                                                     |

| 15  | SEQ_RAM_A15 | read/write | no function                                                         |

| 14  | SEQ_RAM_A14 | read/write | sequencer ram address bit A14                                       |

| 13  | SEQ_RAM_A13 | read/write | sequencer ram address bit A13                                       |

| 12  | SEQ_RAM_A12 | read/write | sequencer ram address bit A12                                       |

|     |             |            |                                                                     |

| 11  | SEQ_RAM_A11 | read/write | sequencer ram address bit A11                                       |

| 10  | SEQ_RAM_A10 | read/write | sequencer ram address bit A10                                       |

| 9   | SEQ_RAM_A9  | read/write | sequencer ram address bit A9                                        |

| 8   | SEQ_RAM_A8  | read/write | sequencer ram address bit A8                                        |

|     |             |            |                                                                     |

| 7   | SEQ_RAM_A7  | read/write | sequencer ram address bit A7 (loaded from the seq. always with "0") |

| 6   | SEQ_RAM_A6  | read/write | sequencer ram address bit A6 (loaded from the seq. always with "0") |

| 5   | SEQ_RAM_A5  | read/write | sequencer ram address bit A5 (loaded from the seq. always with "0") |

| 4   | SEQ_RAM_A4  | read/write | sequencer ram address bit A4 (loaded from the seq. always with "0") |

|     |             |            |                                                                     |

| 3   | SEQ_RAM_A3  | read/write | sequencer ram address bit A3 (loaded from the seq. always with "0") |

| 2   | SEQ_RAM_A2  | read/write | sequencer ram address bit A2 (loaded from the seq. always with "0") |

| 1   | SEQ_RAM_A1  | read/write | sequencer ram address bit A1 (loaded from the seq. always with "0") |

| 0   | SEQ_RAM_A0  | read/write | sequencer ram address bit A0 (loaded from the seq. always with "0") |

Value after Power-up Reset or Reset: 0xFFFF0000

Sequencer ram size: 32K x 48 bit

## 4.7 FASTBUS TIMEOUT REGISTER (R/W)

The Short Timeout is enabled during each primary address and data cycles on FASTBUS if WT is not active.

The Long Timeout is only enabled during FASTBUS arbitration and if WT (wait on FASTBUS) is set during primary address and data cycles.

| bit | name           | R/W        | function                                 |

|-----|----------------|------------|------------------------------------------|

| 31  | reserved       | read only  | "1"                                      |

|     |                |            |                                          |

| 8   | reserved       | read only  | "1"                                      |

|     |                |            |                                          |

| 7   | TIME_LONG_DIS  | read/write | Disable Long Timeout                     |

| 6   | TIME_LONG_2    | read/write | Long Timeout Bit 2                       |

| 5   | TIME_LONG_1    | read/write | Long Timeout Bit 1                       |

| 4   | TIME_LONG_0    | read/write | Long Timeout Bit 0                       |

|     |                |            |                                          |

| 3   | TIME_SHORT_DIS | read/write | Disable Short Timeout                    |

| 2   | TIME_SHORT_2   | read/write | Short Timeout Bit 2 (not used; reserved) |

| 1   | TIME_SHORT_1   | read/write | Short Timeout Bit 1                      |

| 0   | TIME_SHORT_0   | read/write | Short Timeout Bit 0                      |

Value after Power-up Reset, Reset or Key Address "Reset register group LCA2": 0xFFFFFF00

| TIME x2 | TIME x1 | TIME x0 | Short Timeout | Long Timeout |

|---------|---------|---------|---------------|--------------|

| 0       | 0       | 0       | 1.6 us        | 51.2 us      |

| 0       | 0       | 1       | 3.2 us        | 205 us       |

| 0       | 1       | 0       | 6.4 us        | 1.6 ms       |

| 0       | 1       | 1       | 12.8 us       | 12.8 ms      |

| 1       | 0       | 0       |               | 102 ms       |

| 1       | 0       | 1       |               | 8182 ms      |

| 1       | 1       | 0       |               | 6.4 sec      |

| 1       | 1       | 1       |               | 24.8 sec     |

(valid for 40 MHZ Source Clock, 32 MHZ are used !!)

# 4.8 FASTBUS ARBITRATION LEVEL REGISTER (R/W)

| bit | name     | R/W        | function                                          |

|-----|----------|------------|---------------------------------------------------|

| 31  | reserved | read only  | "1"                                               |

|     |          |            |                                                   |

| 8   | reserved | read only  | "1"                                               |

|     |          |            |                                                   |

| 7   | ABIT     | read/write | Assured Access (FAIR)                             |

| 6   | reserved | read/write | reserved                                          |

| 5   | AL5      | read/write | FASTBUS Arbitration Level Bit 5                   |

| 4   | AL4      | read/write | FASTBUS Arbitration Level Bit 4                   |

|     |          |            |                                                   |

| 3   | AL3      | read/write | FASTBUS Arbitration Level Bit 3                   |

| 2   | AL2      | read/write | FASTBUS Arbitration Level Bit 2 (set after reset) |

| 1   | AL1      | read/write | FASTBUS Arbitration Level Bit 1                   |

| 0   | AL0      | read/write | FASTBUS Arbitration Level Bit 0                   |

Value after Power-up Reset, Reset or Key Address "Reset register group LCA2": 0xFFFFF04

# 4.9 FASTBUS PROTOCOL SIGNAL REGISTER (R)

This register is a read only register and gives status information about some FASTBUS signals.

| bit | name     | function                                                                   |

|-----|----------|----------------------------------------------------------------------------|

| 31  | reserved | "1"                                                                        |

|     |          |                                                                            |

| 16  | reserved | "1"                                                                        |

|     |          |                                                                            |

| 15  | FB_RB    | shows the actual status of FASTBUS signal Reset Bus (RB)                   |

| 14  | FB_BH    | shows the actual status of FASTBUS signal Bus Halt (BH)                    |

| 13  | FB_SR    | shows the actual status of FASTBUS signal Service Request (SR)             |

| 12  | ISMINE_L | shows a actual status of the Arbitation Logic                              |

|     |          |                                                                            |

| 11  | FB_GK    | shows the actual status of FASTBUS signal Grant Acknowledge (GK)           |

| 10  | FB_AG    | shows the actual status of FASTBUS signal Arbitration Grant (AG)           |

| 9   | FB_AI    | shows the actual status of FASTBUS signal Arbitration Request Inhibit (AI) |

| 8   | FB_AR    | shows the actual status of FASTBUS signal Arbitration Request (AR)         |

|     |          |                                                                            |

| 7   | FB_EG    | shows the actual status of FASTBUS signal Enable Geographical (EG)         |

| 6   | reserved | "1"                                                                        |

| 5   | FB_AK    | shows the actual status of FASTBUS signal Address Acknowledge (AK)         |

| 4   | FB_DK    | shows the actual status of FASTBUS signal Data Acknowledge (DK)            |

|     |          |                                                                            |

| 3   | FB_WT    | shows the actual status of FASTBUS signal Wait (WT)                        |

| 2   | FB_SS2   | shows the actual status of FASTBUS signal Slave Status Bit2 (SS2)          |

| 1   | FB_SS1   | shows the actual status of FASTBUS signal Slave Status Bit 1 (SS1)         |

| 0   | FB_SS0   | shows the actual status of FASTBUS signal Slave Status Bit 0 (SS0)         |

# 4.10 SEQUENCER FIFO FLAG AND ECL/NIM INPUT REGISTER (R)

This register is a read only register and gives status informations about the AUX\_B42, NIM and ECL inputs and about the Sequencer Fifo Flags.

| bit | name       | function                                               |

|-----|------------|--------------------------------------------------------|

| 31  | reserved   | "1"                                                    |

|     | ••         |                                                        |

| 16  | reserved   | "1"                                                    |

|     |            |                                                        |

| 15  | IN_AUX_B42 | AUXILIARY Connector B42 Input                          |

| 14  | IN_NIM3    | Level Input NIM3                                       |

| 13  | IN_NIM2    | Level Input NIM2                                       |

| 12  | IN_NIM1    | Level Input NIM1                                       |

|     |            |                                                        |

| 11  | IN_ECL4    | Level Input ECL4                                       |

| 10  | IN_ECL3    | Level Input ECL3                                       |

| 9   | IN_ECL2    | Level Input ECL2                                       |

| 8   | IN_ECL1    | Level Input ECL1                                       |

|     |            |                                                        |

| 7   | SEQ2VME_FF | Sequencer to VME Fifo Full Flag (synchronous)          |

| 6   | SEQ2VME_HF | Sequencer to VME Fifo Half Full Flag (asynchronous)    |

| 5   | SEQ2VME_AE | Sequencer to VME Fifo Almost Empty Flag (asynchronous) |

| 4   | SEQ2VME_EF | Sequencer to VME Fifo Empty Flag (synchronous)         |

|     |            |                                                        |

| 3   | VME2SEQ_FF | VME to Sequencer Fifo <b>Full</b> Flag (synchronous)   |

| 2   | VME2SEQ_HF | VME to Sequencer Fifo Half Full Flag (asynchronous)    |

| 1   | VME2SEQ_AE | VME to Sequencer Fifo Almost Empty Flag (asynchronous) |

| 0   | VME2SEQ_EF | VME to Sequencer Fifo <b>Empty</b> Flag (synchronous)  |

(default used Fifos IDT72225: 1K Fifo , Almost Empty is valid if words < 128)

# 4.11 OUT-SIGNAL REGISTER (W)

On the SFI are **two** Out-Signal registers implemented. The first register will be set/cleared by VME cycles and the second will be set/cleared by the Sequencer. The Output Level of the signals NIM\_OUTx, ECL\_Ox and Lx of both register are ored.

Each register is a selective set/clear register. A "0" written into the corresponding bit has no effect. A "1" written into the corresponding bit activates the specified function. A "1" written into both of the set and clear bit is not allowed in the same time (generates toggle function).

# 4.11.1 VME Out-Signal register

| bit | name          | write a "1" function                                 |  |  |  |  |  |  |  |

|-----|---------------|------------------------------------------------------|--|--|--|--|--|--|--|

| 31  | reserved      | no                                                   |  |  |  |  |  |  |  |

| 30  | CLR_AUX_A45   | clear Auxiliary Connector Output A45                 |  |  |  |  |  |  |  |

| 29  | CLR_AUX_A28   | clear Auxiliary Connector Output A28                 |  |  |  |  |  |  |  |

| 28  | CLR_AUX_A10   | clear Auxiliary Connector Output A10                 |  |  |  |  |  |  |  |

|     |               |                                                      |  |  |  |  |  |  |  |

| 27  | reserved      | no                                                   |  |  |  |  |  |  |  |

| 26  | CLR_NIM_OUT 3 | clear NIM Output O3                                  |  |  |  |  |  |  |  |

| 25  | CLR_NIM_OUT 2 | clear NIM Output O2                                  |  |  |  |  |  |  |  |

| 24  | CLR_NIM_OUT 1 | clear NIM Output O1                                  |  |  |  |  |  |  |  |

|     |               |                                                      |  |  |  |  |  |  |  |

| 23  | CLR_ECL_O1    | clear diff. ECL Output O1                            |  |  |  |  |  |  |  |

| 22  | CLR_ECL_O2    | clear diff. ECL Output O2                            |  |  |  |  |  |  |  |

| 21  | CLR_ECL_O3    | clear diff. ECL Output O3                            |  |  |  |  |  |  |  |

| 20  | CLR_ECL_O4    | clear diff. ECL Output O4                            |  |  |  |  |  |  |  |

|     |               | ***************************************              |  |  |  |  |  |  |  |

| 19  | CLR_L4        | clear Led L4 and Testpin output T4 (TTL, low active) |  |  |  |  |  |  |  |

| 18  | CLR_L3        | clear Led L3 and Testpin output T3 (TTL, low active) |  |  |  |  |  |  |  |

| 17  | CLR_L2        | clear Led L2 and Testpin output T2 (TTL, low active) |  |  |  |  |  |  |  |

| 16  | CLR_L1        | clear Led L1 and Testpin output T1 (TTL, low active) |  |  |  |  |  |  |  |

|     | <del></del>   |                                                      |  |  |  |  |  |  |  |

| 15  | reserved      | no                                                   |  |  |  |  |  |  |  |

| 14  | SET_AUX_A45   | set Auxiliary Connector Output A45                   |  |  |  |  |  |  |  |

| 13  | SET_AUX_A28   | set Auxiliary Connector Output A28                   |  |  |  |  |  |  |  |

| 12  | SET_AUX_A10   | set Auxiliary Connector Output A10                   |  |  |  |  |  |  |  |

|     |               |                                                      |  |  |  |  |  |  |  |

| 11  | reserved      | no                                                   |  |  |  |  |  |  |  |

| 10  | SET_NIM_OUT 3 | set NIM Output O3                                    |  |  |  |  |  |  |  |

| 9   | SET_NIM_OUT 2 | set NIM Output O2                                    |  |  |  |  |  |  |  |

| 8   | SET NIM OUT 1 | set NIM Output O1                                    |  |  |  |  |  |  |  |

|     |               |                                                      |  |  |  |  |  |  |  |

| 7   | SET_ECL_O4    | set diff. ECL Output O4                              |  |  |  |  |  |  |  |

| 6   | SET_ECL_O3    | set diff. ECL Output O3                              |  |  |  |  |  |  |  |

| 5   | SET_ECL_O2    | set diff. ECL Output O2                              |  |  |  |  |  |  |  |

| 4   | SET_ECL_O1    | set diff. ECL Output O1                              |  |  |  |  |  |  |  |

|     |               |                                                      |  |  |  |  |  |  |  |

| 3   | SET_L4        | set Led L4 and Testpin output T4 (TTL, low active)   |  |  |  |  |  |  |  |

| 2   | SET_L3        | set Led L3 and Testpin output T3 (TTL, low active)   |  |  |  |  |  |  |  |

| 1   | SET_L2        | set Led L2 and Testpin output T2 (TTL, low active)   |  |  |  |  |  |  |  |

| 0   | SET_L1        | set Led L1 and Testpin output T1 (TTL, low active)   |  |  |  |  |  |  |  |

|     | <u>_</u>      |                                                      |  |  |  |  |  |  |  |

# 4.11.2 Sequencer Out-Signal register (writeable from the sequencer !)

| bit | name          | write a "1" function                                 |

|-----|---------------|------------------------------------------------------|

| 31  | reserved      | no                                                   |

| 30  | reserved      | no                                                   |

| 29  | reserved      | no                                                   |

| 28  | reserved      | no                                                   |

|     |               |                                                      |

| 27  | reserved      | no                                                   |

| 26  | CLR_NIM_OUT 3 | clear NIM Output O3                                  |

| 25  | CLR_NIM_OUT 2 | clear NIM Output O2                                  |

| 24  | CLR_NIM_OUT 1 | clear NIM Output O1                                  |

|     |               |                                                      |

| 23  | CLR_ECL_O1    | clear diff. ECL Output O1                            |

| 22  | CLR_ECL_O2    | clear diff. ECL Output O2                            |

| 21  | CLR_ECL_O3    | clear diff. ECL Output O3                            |

| 20  | CLR_ECL_O4    | clear diff. ECL Output O4                            |

|     |               |                                                      |

| 19  | CLR_L4        | clear Led L4 and Testpin output T4 (TTL, low active) |

| 18  | CLR_L3        | clear Led L3 and Testpin output T3 (TTL, low active) |

| 17  | CLR_L2        | clear Led L2 and Testpin output T2 (TTL, low active) |

| 16  | CLR_L1        | clear Led L1 and Testpin output T1 (TTL, low active) |

|     |               |                                                      |

| 15  | reserved      | no                                                   |

| 14  | reserved      | no                                                   |

| 13  | reserved      | no                                                   |

| 12  | reserved      | no                                                   |

|     |               |                                                      |

| 11  | reserved      | no                                                   |

| 10  | SET_NIM_OUT 3 | set NIM Output O3                                    |

| 9   | SET_NIM_OUT 2 | set NIM Output O2                                    |

| 8   | SET_NIM_OUT 1 | set NIM Output O1                                    |

|     |               |                                                      |

| 7   | SET_ECL_O1    | set diff. ECL Output O1                              |

| 6   | SET_ECL_O2    | set diff. ECL Output O2                              |

| 5   | SET_ECL_O3    | set diff. ECL Output O3                              |

| 4   | SET_ECL_O4    | set diff. ECL Output O4                              |

|     |               |                                                      |

| 3   | SET_L4        | set Led L4 and Testpin output T4 (TTL, low active)   |

| 2   | SET_L3        | set Led L3 and Testpin output T3 (TTL, low active)   |

| 1   | SET_L2        | set Led L2 and Testpin output T2 (TTL, low active)   |

| 0   | SET_L1        | set Led L1 and Testpin output T1 (TTL, low active)   |

## 4.12 VME IRQ Source and MASK REGISTER

Eight interrupt sources are implemented. Each of these interrupt sources can be individually enabled/disabled (cleared) via this J/K register. A J/K register is a selective set/clear register. A "0" written into the corresponding bit has no effect. A "1" written into the corresponding bit activates the specified function. A "1" written into both of the enable-bit and disable (clear)-bit is **not allowed** in the same time (generates a bit toggle function).

| bit | read function        | write a "1" function                        |

|-----|----------------------|---------------------------------------------|

| 31  | "1"                  | no                                          |

|     |                      |                                             |

| 16  | "1"                  | no                                          |

|     |                      |                                             |

| 15  | SEQ_DISABLE_IRQ_FLAG | disable Sequencer DISABLE source            |

| 14  | SEQ_CMD_FLAG         | disable Sequencer CMD Flag source           |

| 13  | SR_IRQ_FLAG          | disable SR source (FASTBUS Service Request) |

| 12  | AUX_B42_IRQ_FLAG     | disable/clear AUX_B42 source                |

|     |                      |                                             |

| 11  | ECL1_IRQ_FLAG        | disable/clear ECL1 IRQ source               |

| 10  | NIM3_IRQ_FLAG        | disable/clear NIM3 IRQ source               |

| 9   | NIM2_IRQ_FLAG        | disable/clear NIM2 IRQ source               |

| 8   | NIM1_IRQ_FLAG        | disable/clear NIM1 IRQ source               |

|     |                      |                                             |

| 7   | SEQ_DISABLE_ENABLE   | enable Sequencer DISABLE source             |

| 6   | SEQ_CMD_FLAG_ENABLE  | enable Sequencer CMD Flag source            |

| 5   | SR_ENABLE            | enable SR source (FASTBUS Service Request)  |

| 4   | AUX_B42_ENABLED      | enable AUX_B42 source                       |

|     |                      |                                             |

| 3   | ECL1_IRQ_ENABLED     | enable ECL1 IRQ source                      |

| 2   | NIM3_IRQ_ENABLED     | enable NIM3 IRQ source                      |

| 1   | NIM2_IRQ_ENABLED     | enable NIM2 IRQ source                      |

| 0   | NIM1_IRQ_ENABLED     | enable NIM1 IRQ source                      |

Value after Power-up Reset, Reset or Key Address "Reset register group LCA2": 0xFFFF0000

## 4.13 VME IRQ LEVEL AND VECTOR REGISTER

This read/write register controls the VME interrupt control logic on the SFI. It is possible to enable/disable the generation of a VME interrupt if an internal VME\_IRQ is set, to determine the VME IRQ Level (IRQ[7..1]) and to determine the 8-bit Status/ID (Interrupt Vector). The type of the Interrupter is **D08(O)**.

| bit | name           | R/W        | function                                                       |

|-----|----------------|------------|----------------------------------------------------------------|

| 31  | reserved       | read only  | "1"                                                            |

|     | ••             |            |                                                                |

| 16  | reserved       | read only  | "1"                                                            |

|     |                |            |                                                                |

| 15  | VME_IRQ        | read only  | "1": VME IRQ is set (internal VME IRQ is set and VME IRQ is    |

|     |                |            | enabled)                                                       |

| 14  | I_VME_IRQ      | read only  | "1": internal VME IRQ is set                                   |

| 13  | reserved       | read only  | "0"                                                            |

| 12  | reserved       | read only  | "0"                                                            |

|     |                |            |                                                                |

| 11  | VME_IRQ_ENABLE | read/write | "0": VME IRQ is disabled; "1": VME IRQ is enabled;             |

| 10  | VME_IRQ_LEV2   | read/write | determines the VME IRQ Level on VME                            |

| 9   | VME_IRQ_LEV1   | read/write | determines the VME IRQ Level on VME                            |

| 8   | VME_IRQ_LEV0   | read/write | determines the VME IRQ Level on VME                            |

|     |                |            |                                                                |

| 7   | Status/ID_bit7 | read/write | Status/ID bit 7; placed on D7 during VME IRQ acknowledge cycle |

| 6   | Status/ID_bit6 | read/write | Status/ID bit 6; placed on D6 during VME IRQ acknowledge cycle |

| 5   | Status/ID_bit5 | read/write | Status/ID bit 5; placed on D5 during VME IRQ acknowledge cycle |

| 4   | Status/ID_bit4 | read/write | Status/ID bit 4; placed on D4 during VME IRQ acknowledge cycle |

|     |                |            |                                                                |

| 3   | Status/ID_bit0 | read/write | Status/ID bit 3; placed on D3 during VME IRQ acknowledge cycle |

| 2   | Status/ID_bit0 | read/write | Status/ID bit 2; placed on D2 during VME IRQ acknowledge cycle |

| 1   | Status/ID_bit0 | read/write | Status/ID bit 1; placed on D1 during VME IRQ acknowledge cycle |

| 0   | Status/ID_bit0 | read/write | Status/ID bit 0; placed on D0 during VME IRQ acknowledge cycle |

Example for VME IRQ Level 5 (IRQ5): VME\_IRQ\_LEV2 = 1

$VME_IRQ_LEV1 = 0$

$VME_IRQ_LEV0 = 1$

Value after Power-up Reset, Reset or Key Address "Reset register group LCA2": 0xFFFF0000

## 6 PANSETIRIUS MURSTER SEQUENCER

Ehight charpteup is sintered edited in the VME interested with the interest of the VME interested in the VME interested in the VME Interrupt Vector (Status/Id) is specified in the VME IRQ Level and Vector register.

As described in much more detail in the following chapters, Fastbus cycles can be executed as VME ADA in the indextruction which will be in the following chapters. Fastbus cycles can be executed as VME ADA in the indextruction of the VME (A24), called Sequencer FIFO key addresses, specify the Fastbus in the following interactions are instructed as a fastbus write operation.

\* Input NIM1: If the NIM1\_IRQ is enabled then the NIM1\_IRQ\_FLAG is set with the leading With the Sequencer FIF@dges\* addresses NIMals imports ib This elaction the factor of the first of t

- \* start autonomous blocktransfer (High speed Fastbus blocktransfer, DK(t) to DS(t) = 35 to 45ns)

- \* InpatlNAM/DMA limitcountername. brookle egabled then the NIM2\_IRQ\_FLAG is set with the leading

- \* load DMA addressdepointer (WMPhins Slampatldress; where the clutareds to items the contract of the clutared stories and the clutared stories are contracted as the clutared stories and the clutared stories are contracted as the clutared stories and the clutared stories are clutared as the clutared stories and the clutared stories are clutared as the clutared stories are clutared as the clutared stories and the clutared stories are clutared as the clutared as the clutared stories are clutared as the clutared as the clutared stories are clutared as the clutar

- \* store DMA wordcontents rice pounde in Sequencer Data Output Fifo to build Event directory

- \* set/clear external signals (NIM, ECL, LEDs)

- \* Input NIM3: If the NIM3\_IRQ is enabled then the NIM3\_IRQ\_FLAG is set with the leading edge\* of the NIM3 input. This flag is cleared with the corresponding disable/clear write cycle.

## 6.1 SEQUENCER ENABLE (ARM)

\* Input ECL1: If the ECL1\_IRQ is enabled then the ECL1\_IRQ\_FLAG is set with the leading After Power-On reset the decuence these disabled appet, all this Fifes are charted twistpostial ector exploiting sequencer with the VME is able disabled appet. The enabled sequencer checks continuously the empty condition of the VME2SEQ Fife. If the sequencer logic detects that the Fife is not empty, then the Associated and Alexed and Exception and the Data Alexed and The Data Alexed and The Associated and the Data Alexed and The Associated and the Data Alexed and The Associated and the Ass

\* Service Request: If the SR\_IRQ (FASTBUS Service Request) is enabled then a SR on FASTBUS Four error condition flagsemerates and antercadal Requirement Status projector in the generation of SR on FASTBUS to be cleared or the Interrupt has to be

\* SEQ\_CMD\_ERRORdisabletis error flag indicates that an invalid sequencer command was written to the VME2SEQ Fifo (Protocol Fifo). For debugging it is possible to read

\* SEQ\_CMD\_FLAG: If the ask Qth CMDt\_Fleeh Gneed command the driven dhe the Last QSeth Ender AProtocol from registers equencer then an internal interrupt is generated. The SEQ\_CMD\_FLAG can be cleared with the VME key address Clear Sequencer

\* SEQ\_PRIM\_ERRORCMDTFlagrror flag indicates that an exeption has occurred during executing a FASTBUS primary address cycle. For debugging it is now possible to read

\* SEQ\_DISABLE: If the disc EQASTS AREA is thrown in terms his other rupt is generated.

(\*\*NSIEQLeDathTgAedGReROTEnsisfTonisfeorm1NTAg invlated (10 M) at canadide prito TND as occurred during executing a

FASTBUS data cycle (secondary address, random data). For debugging it

if is possible 1 td R Q a F L A G F A STBUS Status register 2 to get more on information 2 bar Q the L A G on.

or NIM3 IRQ FLAG

\* SEQ\_DMA\_ERROR: of This er ECT [lag] Rock that an exception has occurred during executing a

on FASTBAISY DRAW blrow temper cycle. For debugging it is possible to read on the FASTBRIS FLAGS register 2 to get more information about the or or one of the second seco

or SEQ\_DISABLE\_IRQ\_FLAG

In case of an error the sequencer has to be reseted to clear the error flags and to clear the Fifos. Then the Wife encer can be enabled again.

## 6.2 SEQUENCER FIFO KEY ADDRESSES

The sequencer commands are written to the VME2SEQ Fifo. The VME2SEQ Fifo consists of a Sequencer Protocol Fifo and a Sequencer Data Input Fifo. The Sequencer Data Input Fifo stores the data (32-bit) and the Protocol Fifo stores the lower part (A15 to A2) of the VME addresses (A32) during the VME write cycle from the CPU to the VME2SEQ Fifo. The sequencer key address (A15 to A2), stored in the Protocol Fifo, determines the action of the sequencer.

General definition of the sequencer key address or sequencer command:

| A15 | A14 | A13 | A12 | A11 | A10 | A9 | A8 | A7 | A6 | A5 | A4 | A3      | A2    | A1 | A0 |

|-----|-----|-----|-----|-----|-----|----|----|----|----|----|----|---------|-------|----|----|

| X   | X   | х   | X   | X   | Х   | X  | X  | F3 | F2 | F1 | F0 | SEQ_CTR | FB_EN | 0  | 0  |

SEQ\_CTR: Sequencer Control action Enable Bit

FB EN: FASTBUS action Enable Bit

F3, F2, F1, F0: Function paramter x: unction depending

## 6.2.1 FASTBUS actions

FASTBUS actions are enabled with SEQ\_CTR = 0 and FB\_EN = 1

| A15 | A14 | A13 | A12 | A11 | A10 | A9  | A8  | A7 | A6 | A5 | A4 | A3 | A2 | A1 | A0 |

|-----|-----|-----|-----|-----|-----|-----|-----|----|----|----|----|----|----|----|----|

| X   | Х   | X   | EG  | RD  | MS2 | MS1 | MS0 | F3 | F2 | F1 | F0 | 0  | 1  | 0  | 0  |

Note that the generation of EG is not vital and even not allowed when trying to pass through Segement interconnects. For test purposes, however, the generation of EG helps to overcome problems due to defective GAC controllers or modules which do not properly take into account the delays of EG when generated by GAC controllers.

| F3 | F2 | F1 | F0 | Function                                                               | Data words defines |

|----|----|----|----|------------------------------------------------------------------------|--------------------|

| 0  | 0  | 0  | 0  | Primary address cycle (include Arbitration)                            | FB Primary Address |

| 0  | 0  | 0  | 1  | Primary address cycle (include Arbitration and holds mastership)       | FB Primary Address |

| 0  | 0  | 1  | 0  | Device Release (Disconnect AS-AK lock)                                 | no                 |

| 0  | 0  | 1  | 1  | Device Release (Disconnect AS-AK lock and releases mastership)         | no                 |

|    |    |    |    |                                                                        |                    |

| 0  | 1  | 0  | 0  | transfer data cycle                                                    | FB Write Data      |

| 0  | 1  | 0  | 1  | transfer data cycle followed by a Device Release (Disconnect)          | FB Write Data      |

| 0  | 1  | 1  | 0  | cleanup data cycle (not impl)                                          | no                 |

| 0  | 1  | 1  | 1  | nop (reserved)                                                         |                    |

|    |    |    |    |                                                                        |                    |

| 1  | 0  | 0  | 0  | nop (reserved)                                                         |                    |

| 1  | 0  | 0  | 1  | load blocktransfer read/write VME address pointer                      | VME Slave Addr.    |

| 1  | 0  | 1  | 0  | load limit counter, clear word counter, start autonomous blocktransfer | Mode/Limit counter |

| 1  | 0  | 1  | 1  | load limit counter and start autonomous blocktransfer                  | Mode/Limit counter |

|    |    |    |    |                                                                        |                    |

| 1  | 1  | 0  | 0  | nop (reserved)                                                         |                    |

| 1  | 1  | 0  | 1  | store address pointer in Sequencer Data Input FiFo (SEQ2VME Fifo)      | no                 |

| 1  | 1  | 1  | 0  | store DMA status and word counter in Sequencer Data Input FiFo         | no                 |

| 1  | 1  | 1  | 1  | store only word counter Sequencer Data Input Fifo (SEQ2VME Fifo)       | no                 |

# 6.2.1.1 Mode register and Limit counter (Sequencer Load)

The sequencer logic loads the Mode register and the Limit counter with the data which are read from the Data Input Fifo (VME2SEQ) during executing the command "load limit counter, clear word counter, start autonomous blocktransfer" before it starts the blocktransfer.

| bit | name        | function                                             |  |  |  |  |  |  |

|-----|-------------|------------------------------------------------------|--|--|--|--|--|--|

| 31  | reserved    | no                                                   |  |  |  |  |  |  |

| 30  | reserved    | no                                                   |  |  |  |  |  |  |

| 29  | reserved    | no                                                   |  |  |  |  |  |  |

| 28  | DIRECT_MODE | enables direct Mode                                  |  |  |  |  |  |  |

|     |             |                                                      |  |  |  |  |  |  |

| 27  | VME_MODE    | enables VME Mode                                     |  |  |  |  |  |  |

| 26  | B64_MODE    | enable VME xBLT64 Blocktransfer (Option, on request) |  |  |  |  |  |  |

| 25  | B32_MODE    | enable VME 32 bit Blocktransfer                      |  |  |  |  |  |  |

| 24  | D32_MODE    | enable VME 32 bit Data cycles                        |  |  |  |  |  |  |

|     |             |                                                      |  |  |  |  |  |  |

| 23  | LIMIT_CNT23 | Limit Counter bit 23 (MSB)                           |  |  |  |  |  |  |

|     |             |                                                      |  |  |  |  |  |  |

|     |             |                                                      |  |  |  |  |  |  |

| 0   | LIMIT_CNT0  | Limit Counter bit 0 (LSB)                            |  |  |  |  |  |  |

The Limit counter controls the maximal length of the FASTBUS blocktransfer if no other stop condition (SS-response or Timeout) is detected.

The blocktransfer stops after <Limit counter > plus one word.

# 6.2.1.2 DMA Status register and Word Counter (Sequencer Store)

The sequencer logic stores the DMA status (blocktransfer) and word counter in the Sequencer Data Output Fifo (SEQ2VME). The VME CPU has to read SEQ2VME Fifo to get this word.

**Note**: The Fifo is only readable, if the Fifo Flag EMPTY is not set. If the Fifo is not empty but the Fifo Flag EMPTY is set, then a read cycle actualize **only** the EMPTY Flag and do not read the data from the Fifo.

| bit | name            | function                                          |  |  |  |  |  |  |  |  |

|-----|-----------------|---------------------------------------------------|--|--|--|--|--|--|--|--|

| 31  | reserved        | "0"                                               |  |  |  |  |  |  |  |  |

| 30  | reserved        | "0"                                               |  |  |  |  |  |  |  |  |

| 29  | DMA_VME_TIMEOUT | indicates a VME TIMEOUT during last DMA           |  |  |  |  |  |  |  |  |

| 28  | DMA_FB_TIMEOUT  | indicates a FASTBUS Timeout during last DMA       |  |  |  |  |  |  |  |  |

|     |                 |                                                   |  |  |  |  |  |  |  |  |

| 27  | DMA_LIMIT       | ndicates that the last DMA stops by Limit Counter |  |  |  |  |  |  |  |  |

| 26  | DMA_SS2         | shows the SS2 bit from last DMA                   |  |  |  |  |  |  |  |  |

| 25  | DMA_SS1         | shows the SS1 bit from last DMA                   |  |  |  |  |  |  |  |  |

| 24  | DMA_SS0         | shows the SS0 bit from last DMA                   |  |  |  |  |  |  |  |  |

|     |                 |                                                   |  |  |  |  |  |  |  |  |

| 23  | WORD_CNT23      | Word counter bit 23 (MSB)                         |  |  |  |  |  |  |  |  |

|     |                 |                                                   |  |  |  |  |  |  |  |  |

|     |                 |                                                   |  |  |  |  |  |  |  |  |

| 0   | WORD_CNT0       | Word counter bit 0 (LSB)                          |  |  |  |  |  |  |  |  |

## 6.2.1.3 FASTBUS command key address assignments

A short overview list for better understanding the FASTBUS action command key addresses is given only (refer to file SFI.H for more details or for use).

```

/* constants for primary address sequencer key addresses */

#define PRIM DSR

(0x0004)

/* Data space logical or geogr. */

#define PRIM_CSR

(0x0104)

/* CSR space logical or geogr.

#define PRIM_DSRM

(0x0204)

/* Data space broadcast

#define PRIM_CSRM

(0x0304)

/* CSR space broadcast

*/

#define PRIM_AMS4

/* MS4 primary address

(0x0404)

*/

#define PRIM_AMS5

(0x0504)

/* MS5 primary address

*/

#define PRIM_AMS6

(0x0604)

/* MS6 primary address

*/

#define PRIM_AMS7

(0x0704)

/* MS7 primary address

/* constants for primary address sequencer key addresses */

#define PRIM_HM_DSR

(0x0014)

/* Data space logical or geogr. and hold Mastership */

/* CSR space logical or geogr. and hold Mastership */

#define PRIM_HM_CSR

(0x0114)

/* Data space broadcast and hold Mastership */

#define PRIM HM DSRM

(0x0214)

#define PRIM_HM_CSRM

(0x0314)

/* CSR space broadcast and hold Mastership */

#define PRIM_EG

(0x1000)

/* to add for setting EG during primary addr. cycle */

#define RNDM_R

(0x0844)

/* random data read */

#define RNDM_W

(0x0044)

/* random data write */

#define SECAD_R

/* secondary address read */

(0x0A44)

/* secondary address write */

#define SECAD_W

(0x0244)

/* random data read and followed disconnect from FB */

#define RNDM_R_DIS

(0x0854)

#define RNDM_W_DIS

(0x0054)

/* random data write and followed disconnect from FB */

#define DISCON

(0x0024)

/* disconnect from FASTBUS; release AS-AK lock */